Mündəricat:

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:44.

- Son dəyişdirildi 2025-01-23 12:54.

AmCoderhttps tərəfindən: //www.linkedin.com/in/mituFollow Müəllif tərəfindən daha çox:

Haqqında: Mitu Raj - Sadəcə Hobbi və Öyrənən - Çip Dizayner - Proqram Yaradıcısı - Fizika və Riyaziyyat Həvəskarı AmCoder haqqında daha çox »

## Bu, sinus və kosinus dalğası yaratmaq üçün CORDIC ALGORITHM -in VHDL tətbiqi üçün Google -da ən çox tıklanan, populyar keçiddir ## Hal -hazırda bir çox aparat səmərəli alqoritm mövcuddur, lakin proqram sistemlərinin üstünlüyünə görə yaxşı bilinmir. uzun illər. CORDIC, müəyyən bir trigonometrik, hiperbolik, xətti və logaritmik funksiyalar daxil olmaqla geniş bir funksiyanı hesablamaq üçün istifadə olunan bir sıra dəyişikliklər və əlavə məntiqdən başqa bir şey olmayan bir alqoritmdir. Bu, kalkulyatorlarda və s. İstifadə olunan alqoritmdir. Beləliklə, sadəcə sadə dəyişdiricilərdən və əlavəçilərdən istifadə edərək, daha az mürəkkəb, lakin DSP gücünə malik bir alqoritm istifadə edərək dizayn edə bilərik. Beləliklə, heç bir xüsusi üzən nöqtə vahidi və ya kompleks riyazi IP istifadə etmədən VHDL və ya Verilogda çılpaq RTL dizaynı kimi dizayn edilə bilər.

Addım 1: VHDL və Modelsim

Burada kordik alqoritm sinüs dalğası və poza dalğası yaratmaq üçün VHDL istifadə edilərək həyata keçirilir. Giriş bucağının sinüs və kosinüsünü böyük dəqiqliklə çıxara bilir. Kod FPGA -da sintez edilə bilər. Modelsim, dizayn və test tezgahını simulyasiya etmək üçün istifadə olunur.

Addım 2: Dizayn və Test Tezgahı üçün VHDL Kodu

İkili ölçmə texnikası, üzən nöqtə nömrələrini təmsil etmək üçün istifadə olunur.

Zəhmət olmasa kod verməzdən əvvəl əlavə edilmiş sənədlər vasitəsilə gedin.

Go thruSimulating cordic_v4.vhd - Dizayn - Giriş 32 bit + işarə bitində açıdır; 0.000000000233 dərəcə giriş dəqiqliyi ilə 0-dan +/- 360 dərəcəyə qədər olan istənilən bucağı işlədə bilər. Giriş verərkən -> MSB işarə bitidir, qalan 32 bit isə böyüklüyü ifadə edir. dəqiqliklə 0.00001526. Nəzərə alın ki, müvafiq sinus və ya cos dəyəri mənfi olarsa, çıxış 2 -nin iltifat şəklində göstərilir. Simulation testb.vhd - Dizayn üçün Test Tezgahı (1) Giriş açıları və çəkmə sıfırlama = '0'. Simulyasiyanın iki addımından sonra "1" və "hamısını işə salın" vəziyyətinə qaytarın. (2) Simulyasiya pəncərəsində günah və cos siqnallarının radiusunu ondalık və format> Analog (avtomatik) olaraq təyin edin. (3) Dalğa formasını görmək üçün uzaqlaşdırın düzgün

Addım 3: Fayllar əlavə olunur

(1) cordic_v4.vhd - Dizayn. (2) testb.vhd - Dizayn üçün test tezgahı.

(3) Bucaq girişlərini məcbur etmək və ikili nəticələri necə çevirmək barədə sənəd.

Yeniləmə: BU DOSYALAR HESAB EDİLMİŞDİR VƏ BAŞQA VERİLMİR. LÜTFEN NÖVBƏTİ ADIMDAN DOSYALARI İSTİFADƏ EDİN

Addım 4: Mini -Cordic IP Core - 16 Bit

Yuxarıdakı tətbiqin məhdudlaşdırılması, bir saat dövrü ərzində hesablamalar apardığı üçün yavaş, daha aşağı işləmə tezliyi. Mini-Cordic IP Core- 16 Bit

- Performansı artırmaq üçün birdən çox dövrə bölüşdürülən kritik yollar.- Daha sürətli- 100 Mhz saata qədər sintez edilmiş FPGA dizaynı.- Daha çox sahə HDL-də optimallaşdırılmış, Daha az aparat. əvvəlki TestBench:

0 ilə 360 dərəcə bucaq girişləri tamamilə avtomatlaşdırılmışdır

Əlavə edilmiş fayllar: 1) mini cordic əsas vhdl faylı 2) mini kordik test tezgahı 3) Mini Cordic IP Core təlimatı 4) Bucaqları necə məcbur etmək və nəticəni çevirmək haqqında sənəd

Hər hansı bir sualınız üçün mənimlə əlaqə saxlaya bilərsiniz:

Mitu Raj

məni izləyin:

poçt: iammituraj@gmail.com

### Toplam yükləmə sayı: 325 01-05-2021 tarixinə qədər ###

### Kod son redaktə: iyul-07-2020 ###

Tövsiyə:

Arduino istifadə edərək İnternetdən istifadə edərək bütün dünyanı idarə et: 4 addım

Arduino istifadə edərək İnternetdən istifadə edərək bütün dünyanı idarə et: Salam, mən Rithikəm. Telefonunuzdan istifadə edərək internetə nəzarət edən bir led quracağıq. Arduino IDE və Blynk kimi proqramlardan istifadə edəcəyik. Bu çox sadədir və uğur qazansanız istədiyiniz qədər elektron komponenti idarə edə bilərsiniz

Python istifadə edərək Raspberry Pi və AIS328DQTR istifadə edərək sürətlənməni izləyin: 6 addım

Python istifadə edərək Raspberry Pi və AIS328DQTR istifadə edərək Sürətləndirməni izləyin: Sürətləndirmə sonsuzdur, düşünürəm ki, Fizikanın bəzi qanunlarına görə. Sahilə çıxan ən sürətli məxluq, bir anda ən yüksək sürətindən istifadə edərək ovunu tutur

Arduino UNO istifadə edərək pilotsuz təyyarə necə etmək olar - Mikrokontrolördən istifadə edərək bir Quadcopter hazırlayın: 8 addım (şəkillərlə)

Arduino UNO istifadə edərək pilotsuz təyyarə necə etmək olar | Mikrokontrolördən istifadə edərək Quadcopter hazırlayın: Giriş Youtube Kanalımı Ziyarət Edin Drone almaq üçün çox bahalı bir gadget (məhsul) təşkil edir. Bu yazıda necə ucuz satacağımı müzakirə edəcəyəm? Ucuz qiymətə öz əlinizlə bunu necə edə bilərsiniz … Yaxşı Hindistanda bütün materiallar (mühərriklər, ESClər

HT12D HT12E istifadə edərək RF 433MHZ Radio İdarəetmə - 433mhz ilə HT12E və HT12D istifadə edərək Rf Uzaqdan İdarəetmə edilməsi: 5 addım

HT12D HT12E istifadə edərək RF 433MHZ Radio İdarəetmə | HT12E və HT12D -dən 433mhz istifadə edərək Rf Uzaqdan İdarəetmə edilməsi: Bu təlimatda sizə HT12E kodlu 433mhz ötürücü qəbuledici modulu istifadə edərək RADIO uzaqdan idarə etməyi göstərəcəyəm. HT12D kod deşifratoru IC. Bu təlimatda çox ucuz komponentləri istifadə edərək məlumat göndərə və ala bilərsiniz: HT

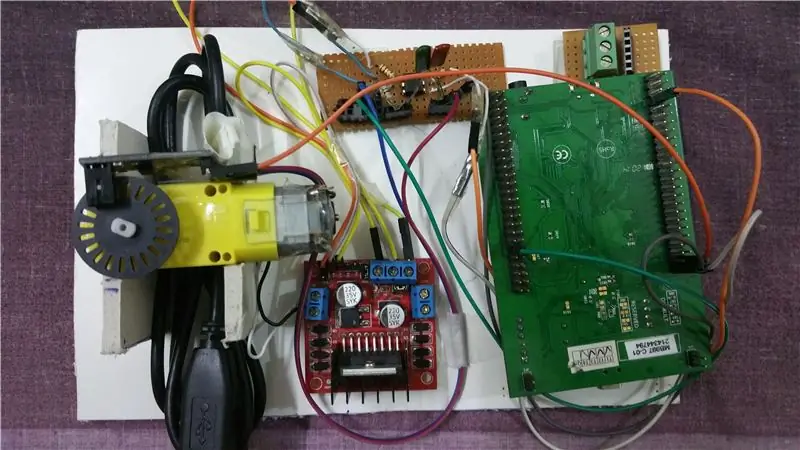

PID Alqoritmi (STM32F4) istifadə edərək DC Motorun Sürət Nəzarəti: 8 Addım (Şəkillərlə)

PID Alqoritmindən (STM32F4) istifadə edərək DC Motorun Sürət Nəzarəti: hər kəsə salam, Bu başqa bir layihə ilə birlikdədir. Bu dəfə MC olaraq STM32F407 -dir. Bu semestr ortası layihəsinin sonudur. Ümid edirik ki, bəyənəcəksiniz. Çox anlayışlar və nəzəriyyə tələb edir, buna görə əvvəlcə bu mövzuya daxil oluruq. Kompüterlərin yaranması ilə