Mündəricat:

- Addım 1: Blok Şeması

- Addım 2: Əməliyyat prinsipi

- Addım 3: Məntiq Tətbiqi

- Addım 4: Çıxış probleminin həlli

- Addım 5: Cihaz Konfiqurasiyası - Matrix0 Circuit

- Addım 6: Cihaz Konfiqurasiyası - SPI Clocking Logic

- Addım 7: Cihaz Konfiqurasiyası - Matrix0 Komponentləri Xüsusiyyətləri

- Addım 8: Cihaz Konfiqurasiyası - Matrix1 Dövrə

- Addım 9: Cihaz Konfiqurasiyası - 3 bitlik İkili Sayıcı

- Addım 10: Cihaz Konfiqurasiyası - 3 -bitlik Məntiq

- Addım 11: Cihaz Konfiqurasiyası - Məntiqlə Rəqəmsal Müqayisə və Müvəqqəti Qeydiyyat

- Addım 12: Cihaz Konfiqurasiyası - Matrix1 Komponentləri Xüsusiyyətləri

- Addım 13: Nəticələr

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:44.

- Son dəyişdirildi 2025-01-23 12:54.

İdarəetmə sistemləri və əlaqəli qurğular, qərəzli xətlər və ya batareyalar kimi çoxlu enerji mənbələri ilə məşğul olur və müəyyən bir dəst arasında ən yüksək (və ya ən aşağı) xətti izləməlidir.

Məsələn, "çox batareya" ilə işləyən bir sistemdə yükün dəyişdirilməsi, sistemin batareya sırası arasındakı minimumu və ya maksimum gərginliyi (xüsusi keçid alqoritminin funksiyası olaraq maksimum və ya min) izləməsini və yükü dinamik olaraq istiqamətləndirməsini tələb edir. real vaxtda ən uyğun mənbə. Alternativ olaraq, sistemin düzgün doldurulması üçün ən aşağı gərginlikli batareyanı müvəqqəti olaraq ayırması lazım ola bilər.

Başqa bir nümunə, hər bir günəş panelinin bir tiltrotate mexanizmi və bir günəş izləmə dövrəsi ilə təchiz olunduğu (günəş panelinin istiqamətləndirilməsi üçün Günəşin mövqeyi haqqında məlumat verən) müasir günəş enerjisi sistemidir. Maksimum gərginlik məlumatı ilə, hər bir günəş paneli mövqeyi, əslində ən yüksək çıxış gərginliyi verən simli panel əsasında dəqiq tənzimlənə bilər və bununla da gücün optimallaşdırılmasının üstün səviyyəsinə çatır.

Prinsipcə maksimum gərginlik izləyicisini tətbiq edə bilən bir neçə fərqli ticarət IC markası (əsasən mikrokontrollerlər) var. Bununla birlikdə, proqramlaşdırma tələb edirlər və qarışıq siqnal həllindən daha ucuzdur. Dialoq GreenPAKTM dizaynının əlavə edilməsi dizaynın əlverişliliyinə, ölçüsünə və modulluğuna müsbət təsir göstərə bilər. Bu dizayn həm analoq, həm də rəqəmsal dövrəni bir çipə birləşdirməyin faydasından istifadə edir.

Bu Təlimat kitabında, səkkiz fərqli qaynaq arasında maksimum (və ya nəhayət min) bir gərginlik tapıcısını həyata keçirmək üçün lazım olan analoq cəbhə və rəqəmsal məntiq tətbiq olunur.

8 kanallı analog max/min gərginlik monitorunu həyata keçirmək üçün SLG46620G istifadə olunur.

Aşağıda, həlli 8 kanallı analog max/min gərginlik monitoru yaratmaq üçün necə proqramlaşdırıldığını anlamaq üçün lazım olan addımları təsvir etdik. Ancaq proqramlaşdırmanın nəticəsini əldə etmək istəyirsinizsə, artıq tamamlanmış GreenPAK Dizayn Faylına baxmaq üçün GreenPAK proqramını yükləyin. GreenPAK İnkişaf Kitini kompüterinizə qoşun və 8 kanallı analog max/min gərginlik monitoru yaratmaq üçün proqramı vurun.

Addım 1: Blok Şeması

Şəkil 1 tətbiq olunan sistemin qlobal diaqramını göstərir.

8 -ə qədər dəyişən gərginlik mənbəyindən ibarət olan bir sıra, digərlərinə nisbətən ən yüksək gərginliyə malik mənbəyi seçə bilən xüsusi bir daxili dizaynla əlaqəli bir GreenPAK -ın ADC modulu ilə əlaqələndirilir. Daxili məntiq bu məlumatları göstərmək və ya daha da işləmək üçün çıxarır.

Dizayn GreenPAK SLG46620G məhsuluna əsaslanır, çünki tətbiq üçün lazım olan bütün analoq və rəqəmsal bina bloklarını özündə birləşdirir. Bu tətbiqdə, sıra GreenPAK IC tərəfindən birbaşa idarə olunan bir ADG508 analog multiplekser vasitəsi ilə taranır.

Çıxış məlumatı, maksimum gərginlikdəki gərginlik mənbəyi nömrəsinə uyğun gələn 3 bitlik rəqəmdir. Bu məlumatı əldə etməyin birbaşa yolu, nömrəni 7 seqmentli bir ekran vasitəsi ilə göstərməkdir. SLG46620G-nin rəqəmsal çıxışını Referansda təsvir edilən GreenPAK həlli kimi 7 seqmentli bir ekran sürücüsünə və ya ümumi 74LS47 IC-ə bağlamaqla asanlıqla əldə etmək olar.

Təqdim olunan sxem maksimum gərginliyi axtarır. Dizaynı minimum bir gərginlik tapıcısına çevirmək üçün, multipleksorun çıxışını 1 V istinad gərginliyindən çıxarmaqla, analog multiplekser və GreenPAK analoq girişi arasında sadə bir ön kondisioner dövrəsi əlavə edilməlidir.

Addım 2: Əməliyyat prinsipi

Dizayn, maksimum gərginlikli mənbəyi seçməyi hədəfləyir, buna görə də son maksimum dəyəri saxlayarkən və girişdəki bir sonrakı dəyərlə (taramada növbəti gərginlik mənbəyinə aid olan) müqayisə edərkən bütün sıra üzərində bir tarama aparılır.

Aşağıda, bütün girişlər boyunca "tarama" və ya "döngə" olaraq tam bir multipleksləmə ardıcıllığına istinad edəcəyik.

İki dəyər arasındakı müqayisə ACMP komponentləri vasitəsi ilə həyata keçirilmir (lakin SLG46620G -də mövcuddur), əksinə dəyərlər rəqəmləşdirildikdən sonra DCMP modulu ilə. Bu, əvvəlcə İstinadda göstərilən inkişaf etmiş və zərif bir texnikadır.

Şəkil 2, SLG46620G -nin bu dizayn üçün necə qurulduğunu göstərir.

Analoq giriş siqnalı, PGA komponenti vasitəsi ilə ADC girişinə 1 qazanc əldə edir. Müxtəlif mənfəət parametrləri, giriş gərginliyini 0-1 V-ə uyğunlaşdırmaq üçün ön kondisioner elektronikası ilə ən yaxşı uyğunluğu tapmaq üçün də mümkündür. GreenPAK ADC modulunun çeşidi.

ADC tək uçlu rejimdə işləyir və analoq siqnalını 8 bitlik rəqəmsal koda çevirir, sonra DCMP moduluna ötürülür. Rəqəmsal kod, ADC/FSM Tamponu olaraq konfiqurasiya edilmiş SPI blokuna da daxil edilir, burada rəqəmsal kod saxlanıla bilər və növbəti nəbz SPI CLK girişinə gələnə qədər dəyişməyəcək. Xüsusi bir məntiq blokunun SPI CLK girişini idarə etdiyinə diqqət yetirin. Düzgün işləməyə cavabdeh olan "əsas" məntiq olduğu üçün bu hissəni daha sonra araşdıracağıq. Yeni rəqəmsal kod SPI modulunda yalnız faktiki maksimum giriş gərginliyinə aid olduqda saxlanılır.

DCMP komponenti, mövcud ADC məlumatlarını SPI blokunda saxlanılan son qaliblə (son tapılan maksimum) müqayisə etmək üçün istifadə olunur. Yeni ADC məlumatları əvvəlkindən daha böyük olduqda OUT+ çıxışında bir nəbz yaradacaq. SPI blokunu yeni qaliblə yeniləmək üçün OUT+ siqnalından istifadə edirik.

Qlobal bir saat siqnalı ADC dönüşümlərini və ümumi vaxtları idarə edir. Bir dönüşüm edildikdən sonra, ADC paralel məlumat çıxışı ilə əlaqələndirilən ADC -nin INT çıxış siqnalının pulsları. INT çıxışını DFF-lərin Matrix1-də tətbiq etdiyi 3 bitlik ikili sayğacı artırmaq üçün də istifadə edirik, bu da üç səbəbdən faydalıdır:

1. Sayğac çıxış xətləri xarici analoq multipleksoruna müraciət edir, beləliklə ADC -ə növbəti giriş gərginliyini verir;

2. Sayma, tarama zamanı müvəqqəti qalibi saxlamaq üçün 3 bitlik reyestrdə (Matrix1-də tətbiq olunur) dondurulur;

3. Tarama tamamlandıqdan sonra ikinci 3 bitlik reyestri (Matrix0-da tətbiq olunur) yeniləmək üçün sayın deşifr edilməsi aparılır.

Addım 3: Məntiq Tətbiqi

ADC modulu ardıcıl olaraq bütün giriş gərginliklərinin çevrilmiş məlumatlarını bir -birinin ardınca qeyri -müəyyən müddətə təmin edir. Multiplexerə 0b111 (ondalık 7) ünvanlandıqda, sayğac 0b000 -ə (ondalık 0) çevrilir və bununla da giriş gərginliklərinin yeni bir taramasına başlayır.

Tarama zamanı paralel məlumat çıxışı etibarlı olduqda ADC INT çıxış siqnalı yaranır. Bu siqnal nəbz vuranda analog multiplekser PGA -ya müvafiq gərginliyi təmin edərək növbəti girişə keçməlidir. Buna görə, ADC INT çıxışı, 3-bit paralel çıxış sözü xarici analog multiplekserə birbaşa müraciət edən Şəkil 2-nin 3-bit İkili Sayğacının birbaşa saat siqnalıdır (Şəkil 1-də “V seçin”).

İndi giriş gərginliklərinin aşağıdakı əlaqələrə malik olduğu bir nümunəyə müraciət edək:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Şəkil 3, maksimum qərar mexanizmində iştirak edən əsas siqnalları əks etdirir.

Nəhayət məlumatlar, INT pulsları ilə sinxron olaraq SPI tampon reyestrinə daxil edildiyindən, SPI tampon məzmununun növbəti ADC dönüşüm nəticəsi ilə müqayisə edildiyi bir müqayisə pəncərəsi mövcuddur. Bu xüsusi vaxt, DCMP çıxışında OUT+ pulslarının yaranması ilə nəticələnir. Bu impulslardan istifadə edərək SPI tampon reyestrinə yeni dəyərlər yükləyə bilərik.

Əvvəlki Şəkilin SPI tampon məlumat xəttindən göründüyü kimi, SPI reyestri hər zaman zamanla 8 giriş arasında ən böyük dəyəri ehtiva edir və yalnız DCMP modulu tərəfindən daha böyük bir dəyər aşkar edildikdə yenilənir (DCMP Sahənin Çıxış+ çıxış xətti, itkin impulslar V2 -nin V5 ilə müqayisədə qeyddə qalmasına səbəb olur).

Addım 4: Çıxış probleminin həlli

Əgər tətbiq olunan məntiq yuxarıda göstərildiyi kimi olsaydı, çıxılmaz vəziyyətə düşəcəyimiz aydındır: sistem yalnız SPI tampon reyestrində saxlanılana uyğun gələndən daha yüksək gərginliyi aşkar edə bilir.

Bu gərginliyin azalması və sonra indiyə qədər daha aşağı olan başqa bir girişin ən yüksək olması halında da keçərlidir: bu heç vaxt aşkar edilməyəcəkdir. aydınlıq.

2 təkrarlama zamanı V3 düşür və V1 faktiki maksimum gərginlikdir. Lakin DCMP modulu nəbz vermir, çünki SPI tampon reyestrində saxlanılan məlumatlar (0,6 V -a uyğun) V1 -ə (0,4 V) uyğun olduğundan daha böyükdür.

Sistem daha sonra "mütləq" maksimum tapıcı kimi çıxış edir və çıxışı düzgün yeniləmir.

Bu problemi aradan qaldırmağın gözəl bir yolu, sistem bütün kanalların tam seçki dövrünü tamamladıqda məlumatları SPI Tampon Reyestrinə yenidən yükləməyə məcbur etməkdir.

Əslində, əgər bu girişdəki gərginlik hələ də ən yüksəkdirsə, heç bir şey dəyişmir və idarəetmə təhlükəsiz şəkildə davam edir (yuxarıdakı Şəkil 4 -ə istinad edərək, 0 və 1 -ci döngə təkrarlanmaları vəziyyətindədir). Digər tərəfdən, təsadüfən həmin girişdəki gərginlik başqa bir girişdən daha aşağı bir dəyərə enərsə, dəyərin yenidən yüklənməsi DCMP moduluna yeni maksimum dəyərlə müqayisə edərkən OUT+ nəbzi çıxarmaq imkanı verir. 2 və 3 -cü döngə təkrarları).

Problemi həll etmək üçün bir məntiq dövrəsi lazımdır. Döngü faktiki maksimum girişə çatdıqda SPI komponentinə bir saat siqnalı yaratmalı və bununla da yenilənmiş məlumat sözünü SPI Tampon Reyestrinə yenidən yükləməyə məcbur etməlidir. Bu, aşağıda 7.2 və 7.6 -cı bölmələrdə müzakirə olunacaq.

Addım 5: Cihaz Konfiqurasiyası - Matrix0 Circuit

SLG46620G, Şəkil 2 -də göstərildiyi kimi iki Matrix blokuna malikdir. Aşağıdakı rəqəmlər müvafiq cihaz konfiqurasiyalarını göstərir.

Dövrün yuxarı hissəsi 3 DFF (DFF0, DFF1 və DFF2) ilə həyata keçirilən "Loop Register" dir. 7-seqmentli bir ekran sürücüsünə "tarifi" nin ikili nömrəsini, son taramada ən yüksək gərginliyə malik girişi göndərmək üçün giriş multipleksorunun hər döngəsindən sonra yenilənir. Həm DFF -lər üçün saat, həm də məlumatlar Matrix1 -də sırasıyla P12, P13, P14 və P15 portu vasitəsilə həyata keçirilən məntiqdən gəlir.

Alt hissə, Pin 8 -də girişi olan və x1 qazanclı PGA ilə analog ön ucdur. ADC INT çıxışı həm SPI -nin saat məntiqinə, həm də P0 portu vasitəsilə Matrix1 -ə gedir, burada sayğac üçün saat siqnalı kimi xidmət edəcək.

ADC və SPI paralel məlumat çıxışları, Matrix1 -də DCMP komponentinə qoşulmaq üçün NET11 və NET15 olaraq etiketlənir.

Addım 6: Cihaz Konfiqurasiyası - SPI Clocking Logic

Daha əvvəl "Məntiq Tətbiqi" bölməsində qeyd edildiyi kimi, SPI Tampon Reyestri hər dəfə faktiki saxlanan dəyərlə yeni ADC dönüşüm məlumatları arasındakı müqayisə DCMP OUT+ çıxışında bir nəbz yaradan zaman yenilənir.

Bu siqnal ADC INT çıxışı ilə VƏ redaktə edildikdə siqnal bütövlüyü təmin edilir. Bu, hər hansı bir sıçrayış və yanlış tetiklemenin qarşısını alır.

Çıxış vəziyyətlərini atlamaq üçün, döngə real qalib məlumatlarına çatdıqda SPI Tamponunun yenilənməsi lazım olduğunu da vurğuladıq.

Düzgün SPI saatı üçün oyunda üç siqnal var:

1. ADC INT çıxışı (LUT0-IN1)

2. DCMP OUT+ çıxışı (P10 portu vasitəsilə LUT0-IN0)

3. Say Latch siqnalına bərabərdir (P11 portu vasitəsilə LUT0-IN2)

İlk ikisi AND-ed və hər ikisi də LUT0-da ikincisi ilə OR-ed, tətbiqləri Şəkil 6-da olduğu kimi qurulmuşdur.

Addım 7: Cihaz Konfiqurasiyası - Matrix0 Komponentləri Xüsusiyyətləri

Şəkillər 7-10-da Matrix0-a məxsus qalan komponentlərin xüsusiyyət pəncərələri göstərilir.

Addım 8: Cihaz Konfiqurasiyası - Matrix1 Dövrə

Addım 9: Cihaz Konfiqurasiyası - 3 bitlik İkili Sayıcı

Dövrün yuxarı hissəsində məntiq elementləri, əsasən də artıq müzakirə edildiyi kimi ADC INT çıxışı ilə işlənmiş 3 bitlik ikili sayğac var. Bu sayğac, Şəkil 12 -də göstərilən olduqca "standart" bir sxem ilə həyata keçirilir.

Bu sayğac dizaynımızda Flip-Flops DFF9, DFF10, DFF11 və INV1, LUT4, LUT8 vasitəsi ilə həyata keçirilir. DFF9 çıxışı LSB, DFF11 isə Şəkil 13 -də göstərildiyi kimi MSB -dir.

LUT4, XOR olaraq konfiqurasiya edilir, LUT8 isə Şəkil 12-də AND-XOR məntiqini yerinə yetirir.

Sayğac çıxışları, xarici Analog Çoxlayıcıya müraciət etmək üçün üç rəqəmsal çıxış pininə gedir.

LUT10, tarama başa çatdıqda sayğacın kodunu deşifr edir və nəbzi DLY8 və P12 portu vasitəsilə Matrix0 -a ötürür. Bu sadəcə sayğacın çıxışlarını AND-ın daxil edilməsi ilə həyata keçirilir, beləliklə 7 dec (0b111 ikili, döngənin sonu) rəqəminin deşifr edilməsi.

Addım 10: Cihaz Konfiqurasiyası - 3 -bitlik Məntiq

Şəkil 15, döngənin cari "qalib" ünvanda təkrarlandığını aşkar etmək üçün istifadə olunan dövrə göstərir. Bu vəziyyətdə, artıq müzakirə edildiyi kimi, rəqəmsal bir nəbz mümkün bir çıxılmaz vəziyyəti həll etmək üçün mövcud ADC nəticəsini yenidən yükləməyə məcbur etməlidir.

"Qalib" ünvanı Matrix1 -in müvəqqəti reyestrində saxlanılır (aşağıya baxın), cari ünvan isə ikili sayğac tərəfindən verilir.

XNOR qapıları hər iki giriş bərabər olduqda doğru (məntiq 1 və ya 'yüksək') çıxış təmin edir. Və bütün bitlər üçün (LUT9) bu siqnal hər iki ikili kod eyni olduqda bizə bir nəbz verir. Paritet yoxlayıcısı olaraq XOR qapıları haqqında ətraflı məlumatı Referansda tapa bilərsiniz.

'Counter-equals-Latch' siqnalı P11 portu vasitəsilə Matrix0-a ötürülür.

Addım 11: Cihaz Konfiqurasiyası - Məntiqlə Rəqəmsal Müqayisə və Müvəqqəti Qeydiyyat

Şəkil 11-in aşağı hissəsi (Şəkil 16-da vurğulanmışdır) bu dizaynın qərar verən hissəsi olan DCMP blokunu göstərir.

DFF6, 7 və 8, döngə işləyərkən müvəqqəti giriş nömrəsini "qalib" saxlamaq üçün 3 bitlik bir qeyd yaradır. Flip-Floplara giriş, aydınlıq naminə atlanılan Şəkil 11-in qlobal Matrix1 sxemində göründüyü kimi 3 bitlik ikili sayğac çıxışlarıdır.

Bu reyestrin nəticələri birbaşa 7 seqmentli ekranı idarə edə bilməz, çünki burada saxlanılan dəyər tarama zamanı dəyişir və yalnız taramanın sonunda "etibarlı" sayılmalıdır.

Bu səbəbdən, müvəqqəti qeyd çıxışları matrisalararası P13, P14 və P15 portları vasitəsi ilə Matrix0 Loop Register-ə qoşulur.

Şəkil 16-da müşahidə etmək vacibdir ki, ADC-SPI qeydləri yeni bir maksimum tapdıqda müvəqqəti qeydiyyatın DCMP OUT+ çıxışı ilə saatlandığını müşahidə etmək vacibdir.

Eyni OUT+ siqnalı P10 portu vasitəsilə Matrix0, SPI CLK Logic -ə ötürülür.

Addım 12: Cihaz Konfiqurasiyası - Matrix1 Komponentləri Xüsusiyyətləri

Rəqəmlər 17-19 Matrix1-ə aid olan komponentlərin xüsusiyyət pəncərələrini göstərir.

Addım 13: Nəticələr

Həyata keçirilməsini sınamaq üçün 8 analoq giriş gərginliyinin TrimPots ilə bir sıra rezistor bölücüləri ilə əldə edildiyi bir qiymətləndirmə lövhəsi prototipi qurulmuşdur (Şəkil 20 -də göstərildiyi kimi).

Tək təchizatla (12 V) işləyə bilən bir hissə olan ADG508 istifadə olunan multiplekserdir.

7 seqmentli ekran sürücüsü 74LS47-dir. Paralel bir giriş sözünü deşifr edir və 7-seqmentli ümumi anodlu ekranı birbaşa idarə edir.

Qiymətləndirmə lövhəsi, Şəkil 21-də göstərildiyi kimi genişləndirici konnektorunda birbaşa GreenPAK İnkişaf etdirmə Platformasına qoşulmaq üçün 2x10 düz bucaqlı bir konnektora malikdir.

GreenPAK Ətraflı İnkişaf Platforması ilə birləşmə sürətli bir yoxlama üçün siqnalların ölçülməsini çox asanlaşdırır. Məsələn, Şəkil 22, HP 54620A Məntiq Analizatoru tərəfindən çəkilmiş bir sıra siqnalları (müvafiq olaraq CLOCK, ADC INT çıxışı və DCMP OUT+ çıxışı) göstərir. Dalğa formaları, OUT+ siqnalının yüksələn kənarı ilə tetiklenir ('A> B' olaraq qeyd olunur), buna görə də analoq girişlər arasında yeni bir maksimum Gərginlik aşkar edildikdə bu dalğa formasıdır. Əslində, Şəkil 22 -də göstərilən müvafiq gərginliyi artırmaq üçün Qiymətləndirmə Şurasının TrimPotlarından birini fırladaraq əldə edilmişdir.

Şəkil 23, Qiymətləndirmə Şurasının sxemini göstərir.

Nəticə

Bu Təlimat kitabında, çox kanallı idarəetmə sistemlərinə ümumi bir əlavə olaraq istifadə ediləcək səkkiz kanallı maksimum (və ya min) bir gərginlik tapıcısını tətbiq etdik. Təqdim olunan yanaşma GreenPAK komponentlərinin qabaqcıl xüsusiyyətlərindən istifadə edir və bir çip analoq və rəqəmsal funksiyalara necə inteqrasiya oluna biləcəyini göstərir. Tətbiqin ölçüsünü və dəyərini azaltmaq üçün bir neçə kommersiya IC -ni Dialog GreenPAK ilə əvəz etmək olar.

Tövsiyə:

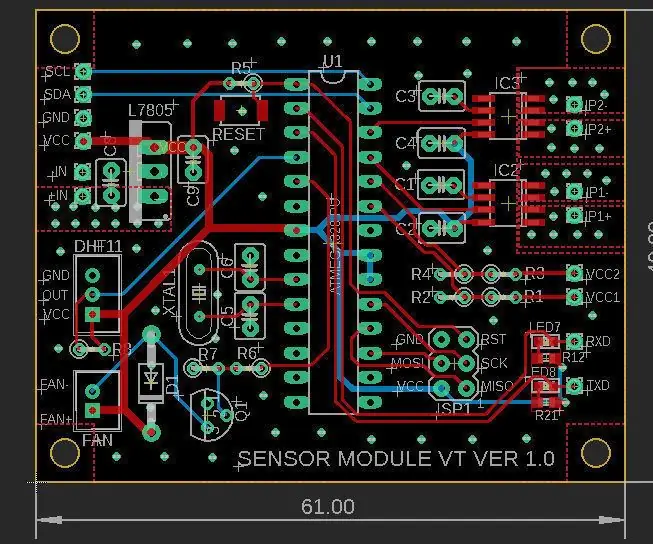

Arduino İkili Kanallı Gərginlik Sensor Modulu: 8 addım

Arduino İkili Kanallı Gərginlik Sensor Modulu: Təlimatlı bir yazı yazmağımdan bir neçə il keçdi, geri dönməyin vaxtı olduğunu düşünürdüm. Tezgahımın enerji təchizatı ilə əlaqə qura biləcəyim bir gərginlik sensoru qurmaq istəyirdim. İki kanallı dəyişən enerji təchizatım var, n

Yüksək Gərginlikli Batareyalar üçün Gərginlik Monitoru: 3 Adım (Şəkillərlə birlikdə)

Yüksək Gərginlikli Batareyalar üçün Gərginlik Monitoru: Bu təlimatda sizə elektrik lövhəm üçün batareya gərginliyi monitorunu necə qurduğumu izah edəcəyəm. İstədiyiniz kimi quraşdırın və batareyanıza yalnız iki tel bağlayın (Gnd və Vcc). Bu təlimat, batareyanızın gərginliyinin 30 voltdan artıq olduğunu güman edirdi

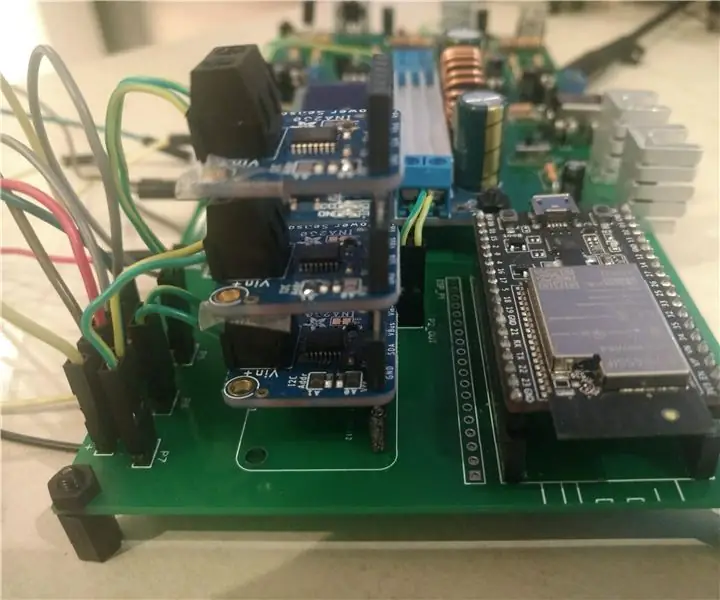

Çox kanallı Wifi Gərginlik və Akım Ölçən: 11 Adım (Şəkillərlə birlikdə)

Çox kanallı Wifi Gərginlik və Cərəyan Ölçən: Çörək taxtası taxarkən tez-tez dövrənin müxtəlif hissələrini eyni anda izləmək lazımdır. Multimetr problarını bir yerdən başqa yerə yapışdırmaqdan çəkinməmək üçün çox kanallı bir gərginlik və cərəyan sayğacını dizayn etmək istədim. Ina260 lövhəsi

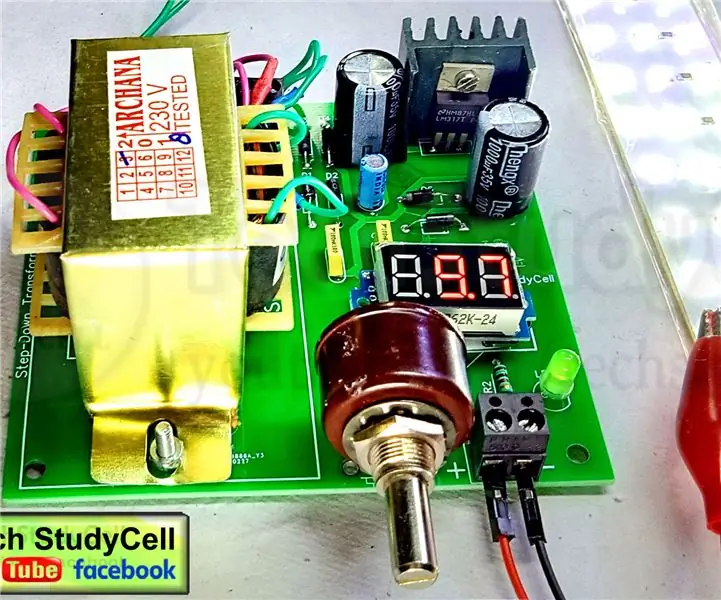

LM317 gərginlik tənzimləyicisini istifadə edərək tənzimlənən gərginlik DC enerji təchizatı: 10 addım

LM317 gərginlik tənzimləyicisini istifadə edərək tənzimlənən gərginlik DC enerji təchizatı: Bu layihədə, LM317 güc təchizatı dövrə diaqramı ilə LM317 IC istifadə edərək sadə tənzimlənən gərginlikli DC enerji təchizatı hazırladım. Bu dövrənin daxili bir körpü düzəldicisi olduğu üçün girişdə birbaşa 220V/110V AC təchizatı bağlaya bilərik

PC və ya Ev Teatrı üçün 8 Kanallı Analog Gücləndirici: 12 Adım (Şəkillərlə)

PC və ya Ev Teatrı üçün 8 Kanal Analog Gücləndirici: Bu mənim ilk təlimatımdır. Ayrı bir analog çıxışı olan bir kompüter və ya səs sistemi üçün 8 kanallı bir gücləndiricinin necə hazırlanacağını öyrədəcəyəm, onu masa üstü kompüterimdə film izləmək, HD musiqi dinləmək və oyun oynamaq üçün istifadə etdim