Mündəricat:

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:45.

- Son dəyişdirildi 2025-01-23 12:54.

Bu təlimatda RTL -də sadə bir VGA Controller dizayn edəcəyik. VGA Controller, VGA displeylərini idarə etmək üçün hazırlanmış rəqəmsal bir sxemdir. Görüntülən çərçivəni təmsil edən Çərçivə Tamponundan (VGA Yaddaş) oxuyur və görüntü məqsədi ilə lazımi məlumatları və sinxronizasiya siqnallarını yaradır.

Verilog/Sistem verilog kodu axtarırsınızsa: Verilogdakı blogum VGA Controller və Video Sistemini ziyarət edin.

Addım 1: VGA nəzarətçisinin interfeysi

VGA nəzarətçisindəki əsas interfeys siqnalları aşağıda verilmişdir

- Pixel Saat və ya VGA Saatı

- HSYNC və VSYNC siqnalları

Seçilmiş VGA ekranı üçün əvvəlcə onu idarə etmək üçün lazım olan Pixel Clock tezliyini hesablamalısınız. 3 parametrdən asılıdır: Ümumi Yatay Piksellər, Ümumi Şaquli Piksellər, Ekran Yeniləmə Hızı.

Tipik olaraq, F = THP * TVP * Yeniləmə Hızı

Əlavə edilmiş RAR -da müxtəlif VGA ekranları üçün lazım olan piksel saat sənədlərini tapın.

HSYNC və VSYNC siqnalları Pixel saatından yaradılır. HSYNC və VSYNC siqnallarının vaxtı parametrlərin sayından asılıdır: Üfüqi və Şaquli Cəbhə, Üfüqi və Şaquli Aralıq, Yatay və Şaquli Ekran Pikselləri, Yatay və Şaquli Sinx Pulse Genişlikləri və Qütbləri.

Bu parametrlər seçilmiş VGA ekranı üçün standartlaşdırılmışdır. Bu sənədləri əlavə edilmiş RAR -da tapın.

Bu parametrlər VGA Controller IP -də konfiqurasiya edilə bilən parametrlərdir.

Addım 2: VGA Nəzarətçisini VGA Ekranı ilə birləşdirin

Şəkil VGA Controller -in VGA ekranı ilə necə birləşdiriləcəyini göstərir. Sistemi tamamlamaq üçün daha iki komponentə ehtiyacınız var:

- Çərçivə Tamponu: Görüntülən çərçivəni tutan yaddaş.

- Video DAC: RGB rəqəmsal məlumatlarını çevirən və uyğun gərginlik səviyyəsində RGB analoq siqnalları ilə VGA Ekranı idarə edən DAC.

Ən sadə və populyar Video DAC -lərdən biri ADV7125 -dir. RGB rəqəmsal sözlərini 0-0.7 V analog siqnallarına çevirən və VGA displeyini idarə edən 8 bitlik DAC-dır.

Addım 3: Çərçivə Tampon Dizaynı

Göstəriləcək görüntünü 'saxlayan' yaddaşdır. Adətən bir RAM və ya bəzən bir ROMdur. Bir görüntünü təmsil etmək üçün bir çərçivə tamponunun necə dizayn ediləcəyini müzakirə edəcəyik. Çərçivə tamponu bu rəqəmsal məlumatı VGA Controller -in əmri ilə Video DAC -a ötürür.

Əvvəlcə lazım olan piksel dərinliyinə qərar verməliyik. Görüntünün keyfiyyətinə, bir pikselin təmsil edə biləcəyi rənglərin müxtəlifliyinə qərar verir. 8 bitlik DAC üçün bir pikselin əsas rəng komponentlərini təmsil etməliyik: R, G və B hər birini 8 bitdə. Bir pikselin 24 bit olması deməkdir.

Hər piksel Frame Buffer yaddaş yerlərində bitişik şəkildə saxlanılır.

Tutaq ki, göstəriləcək şəkil 800x600 pikseldir.

Buna görə Frame Buffer 800x600 = 480000 x 24 bit yaddaşa ehtiyac duyur

Yaddaşın ümumi ölçüsü təxminən 800x600x24 = 1400 kB -dir.

Qara və ağ şəkil varsa, 800x600x1 = 60 kB təxminən.

Blok RAM -lər, bəlkə də Xilinx FPGA -da bir Çərçivə Tamponunu təmsil etmək üçün istifadə olunur.

Addım 4: Qeydlər

- Seçilmiş DAC -dan asılı olaraq VGA Controller -də əlavə siqnallara ehtiyac var. ADV7125 istifadə etdim.

- VGA ekranı sürməzdən əvvəl VSYNC və HSYNC-də flip-floplar vasitəsilə dövr gecikmələri əlavə edin. Bunun səbəbi DAC və Yaddaş gecikmələridir. Piksel siqnalları HSYNC və VSYNC ilə sinxronlaşdırılmalıdır. Mənim vəziyyətimdə 2 dövr gecikmə idi.

- Verilən ölçüdə Çərçivə Tamponu blok ölçüsünün məhdudlaşdırılması səbəbindən FPGA üzərində tərtib edilə bilmirsə, görüntünü əks etdirmək üçün daha kiçik yaddaşdan istifadə edin və kodu tam çərçivənin deyil, mövcud yaddaşın hüdudunda gəzmək üçün kodu düzəldin. Bu, eyni görüntünü bütün ekran boyunca dəfələrlə təkrarlayacaq. Başqa bir üsul, hər bir görüntünün daha az qətnamə ilə bütün görüntünü tam ekranda göstərmək üçün təkrarlandığı piksel ölçüsüdür. Bu, koddakı ünvan artım məntiqini düzəltməklə edilə bilər.

- IP bütün FPGA-lar arasında tamamilə portativdir və Virtex-4 FPGA-da 100 MHz-ə qədər təsdiqlənmiş vaxtdır.

Addım 5: Əlavə edilmiş fayllar

RAR ehtiva edir:

- VGA nəzarətçi kodu

- PDF formatında VGA.

Tövsiyə:

VHDL-də Sadə Dörd Yollu Assosiativ Keş Nəzarətçisinin Dizaynı: 4 Addım

VHDL-də Sadə Dörd Yollu Assosiativ Önbellek Nəzarətçisinin Dizaynı: Əvvəlki təlimatımda sadə birbaşa xəritələnmiş önbellek nəzarətçisinin necə dizayn ediləcəyini gördük. Bu dəfə bir addım irəli gedirik. Sadə dörd yollu assosiativ önbelleğe nəzarətçi dizayn edəcəyik. Üstünlük? Daha az qaçırma dərəcəsi, amma mükəmməlliyə görə

VHDL -də proqramlaşdırıla bilən kəsilmə nəzarətçisinin dizaynı: 4 addım

VHDL -də proqramlaşdırıla bilən kəsilmə nəzarətçisinin dizaynı: Bu bloqda aldığım cavablar məni boğur. Bloqumu ziyarət etdiyiniz və biliklərimi sizinlə bölüşməyim üçün motivasiya etdiyiniz üçün təşəkkür edirəm. Bu dəfə bütün SOC -da gördüyümüz başqa bir maraqlı modulun dizaynını təqdim edəcəyəm - Interrupt C

VHDL -də sadə bir önbellek nəzarətçisinin dizaynı: 4 addım

VHDL -də Sadə Keş Nəzarətçisinin Dizaynı: Mən bu təlimatı yazıram, çünki bir önbelleğe nəzarətçi dizaynını öyrənmək və dizayn etməyə başlamaq üçün VHDL -ə istinad etmək çətin idi. Beləliklə, özüm sıfırdan bir önbelleğe nəzarətçi hazırladım və FPGA -da uğurla sınadım. Məndə p

Sadə və asan addımlarla PCB dizaynı: 30 addım (şəkillərlə)

Sadə və Asan Adımlarla PCB Dizaynı: SALAM DOSTLAR PCB dizaynını öyrənmək istəyənlər üçün çox faydalı və asan təlimatı başlaya bilərik

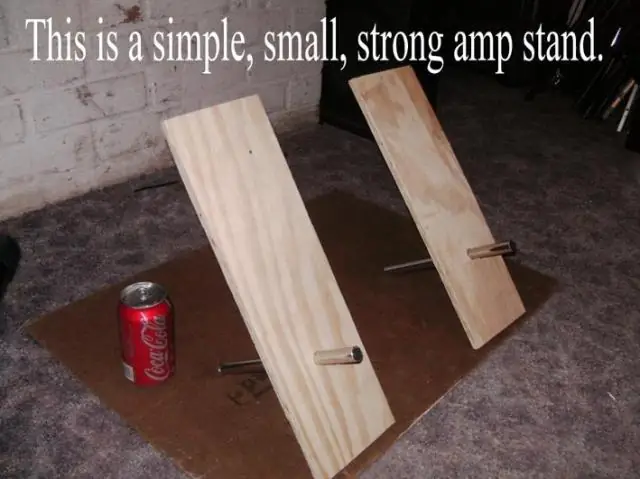

Gitara Amp Tilt Standı - "Afrika Kreslosu" Dizaynı - Sadə, Kiçik, Güclü, Asan, Pulsuz və ya Real Ucuz: 9 Addım

Gitara Amp Tilt Standı - "Afrika Kreslosu" Dizaynı - Sadə, Kiçik, Güclü, Asan, Pulsuz və ya Real Ucuz: Gitara Amp Tilt Standı - Çox Asan - sadə, kiçik, güclü, pulsuz və ya real ucuz. Bütün ölçülü amperlər üçün, hətta ayrı başlıqlı böyük kabinetlər. İstədiyiniz hər hansı bir avadanlıq üçün lazım olan ölçüdə lövhələr və borular hazırlayın