Mündəricat:

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:45.

- Son dəyişdirildi 2025-01-23 12:54.

VHDL kodunu öyrənmək və önbelleğe nəzarətçi hazırlamağa başlamaq üçün bir az çətin olduğunu gördüyüm üçün bu təlimatı yazıram. Beləliklə, özüm sıfırdan bir önbelleğe nəzarətçi hazırladım və FPGA -da uğurla sınadım. Burada sadə birbaşa xəritələnmiş önbellek nəzarətçisini təqdim etdim, eyni zamanda önbelleği yoxlamaq üçün bütün bir Prosessor-Yaddaş Sistemini modelləşdirdim. Ümid edirəm uşaqlar, bu önəmli məlumatı öz önbellek kontrollerlerinizi dizayn etmək üçün bir faydalı olaraq tapacaqsınız.

Addım 1: Xüsusiyyətlər

Dizayn edəcəyimiz Cache Controller -in əsas xüsusiyyətləri bunlardır:

- Birbaşa Xəritəçəkmə. (Assosiativ Mapping Cache Controller axtarırsınızsa bu linkə daxil olun)

- Tək Banklı, Bloklama Önbelleği.

- Yazma xitlərində yazma siyasəti.

- Yazma əldən verməmək üçün Yazma Yoxlama və ya Ətrafına Yazma Siyasəti.

- Yazı Tamponu və ya digər optimallaşdırmalar yoxdur.

- Tag Array daxil edilmişdir.

Bundan əlavə, bir Önbellek Yaddaşı və Əsas Yaddaş Sistemi də dizayn edəcəyik.

Önbellek Yaddaşının standart (konfiqurasiya edilə bilən) xüsusiyyətləri:

- 256 Bayt Tək Banklı Önbellek.

- 16 Önbellek Xətti, hər Cache Xətti (Blok) = 16 Bayt.

Əsas Yaddaşın xüsusiyyətləri:

- Sinxron Oxuma/Yazma Yaddaşı.

- Çox banklı Interleaved Yaddaş - dörd yaddaş bankı.

- Hər bir bankın ölçüsü = 1 kB. Beləliklə, ümumi ölçü = 4 kB.

- 10 bitlik ünvan avtobusu ilə Word (4 bayt) ünvanlı yaddaş.

- Oxumaq üçün daha yüksək bant genişliyi. Məlumat Genişliyi = 16 Bayt bir saat dövrəsində oxuyun.

- Məlumat Genişliyi = 4 Bayt yazın.

DİQQƏT: 4 tərəfli assosiativ önbelleğe nəzarətçi dizaynı axtarırsınızsa, yeni təlimatımı yoxlayın

Addım 2: Bütün Sistemin RTL Görünüşü

Üst Modulun tam RTL nümayişi Şəkildə göstərilmişdir (prosessor istisna olmaqla). Avtobuslar üçün standart xüsusiyyətlər:

- Bütün Məlumat Avtobusları 32 bitlik Avtobuslardır.

- Ünvan Avtobusu = 32 bitlik Avtobus (Ancaq burada yalnız 10 bit Yaddaş tərəfindən ünvanlanır).

- Məlumat Bloku = 128 bit (Oxunmaq üçün Geniş Bant Genişliyi Avtobusu).

- Bütün komponentlər eyni saatla idarə olunur.

Addım 3: Ətraf mühiti sınayın

Üst Modul, boru kəmərsiz bir prosessoru modelləşdirən bir Test Bench istifadə edərək sınaqdan keçirildi (Çünki bütün prosessorun dizaynı heç də asan deyil !!). Test Bench tez -tez Yaddaşa Məlumat Oxu/Yazma sorğuları yaradır. Bu, prosessor tərəfindən icra edilən bütün proqramlarda ümumi olan "Yüklə" və "Saxla" təlimatlarını lağa qoyur. Test nəticələri Cache Controller funksiyasını uğurla yoxladı. Aşağıda müşahidə olunan test statistikası verilmişdir:

- Bütün Oxu/Yaz Miss və Hit siqnalları düzgün yaradılmışdır.

- Bütün Məlumatların Oxunması/Yazılması əməliyyatları uğurlu alındı.

- Məlumat uyğunsuzluğu/uyğunsuzluq problemi aşkarlanmadı.

- Dizayn bir Maxm üçün uğurla təsdiqləndi. İşləmə tezliyi = Xilinx Virtex-4 ML-403 lövhəsində 110 MHz (bütün sistem), yalnız Cache Controller üçün 195 MHz.

- Blok RAM -lar Əsas Yaddaş üçün çıxarıldı. Bütün digər seriallar LUT -lərdə tətbiq edilmişdir.

Addım 4: Əlavə edilmiş fayllar

Aşağıdakı fayllar bu blogla birlikdə burada əlavə olunur:

- Cache Controller, Cache Data Array, Ana Yaddaş Sisteminin. VHD faylları.

- Test bench.

- Cache Controller sənədləri.

Qeydlər:

- Burada təqdim olunan Önbellek Denetleyicisinin xüsusiyyətlərini tam başa düşmək üçün sənədlərdən keçin.

- Koddakı hər hansı bir dəyişiklik digər modullardan asılıdır. Buna görə dəyişikliklər ağıllı şəkildə aparılmalıdır. Verdiyim bütün şərhlərə və başlıqlara diqqət yetirin.

- Hər hansı bir səbəbdən, Blok RAM -lar Əsas Yaddaş üçün nəticə çıxarmırsa, yaddaşın ölçüsünü azaldın, sonra fayllar arasında ünvan avtobusu genişliyində dəyişikliklər edin və s. Eyni yaddaş ya LUT -lərdə, ya da Paylanmış RAM -da tətbiq oluna bilər. Bu, marşrutlaşdırma vaxtına və mənbələrə qənaət edəcəkdir. Və ya xüsusi FPGA sənədlərinə gedin və Block RAM üçün uyğun kodu tapın və buna uyğun olaraq kodu düzəldin və eyni ünvan avtobus genişliyi xüsusiyyətlərindən istifadə edin. Altera FPGA'lar üçün eyni texnika.

Tövsiyə:

VHDL-də Sadə Dörd Yollu Assosiativ Keş Nəzarətçisinin Dizaynı: 4 Addım

VHDL-də Sadə Dörd Yollu Assosiativ Önbellek Nəzarətçisinin Dizaynı: Əvvəlki təlimatımda sadə birbaşa xəritələnmiş önbellek nəzarətçisinin necə dizayn ediləcəyini gördük. Bu dəfə bir addım irəli gedirik. Sadə dörd yollu assosiativ önbelleğe nəzarətçi dizayn edəcəyik. Üstünlük? Daha az qaçırma dərəcəsi, amma mükəmməlliyə görə

VHDL -də proqramlaşdırıla bilən kəsilmə nəzarətçisinin dizaynı: 4 addım

VHDL -də proqramlaşdırıla bilən kəsilmə nəzarətçisinin dizaynı: Bu bloqda aldığım cavablar məni boğur. Bloqumu ziyarət etdiyiniz və biliklərimi sizinlə bölüşməyim üçün motivasiya etdiyiniz üçün təşəkkür edirəm. Bu dəfə bütün SOC -da gördüyümüz başqa bir maraqlı modulun dizaynını təqdim edəcəyəm - Interrupt C

VHDL və Verilogda sadə bir VGA nəzarətçisinin dizaynı: 5 addım

VHDL və Verilogda Sadə VGA Nəzarətçisinin Dizaynı: Bu təlimatda RTL -də sadə bir VGA Nəzarətçisi dizayn edəcəyik. VGA Controller, VGA ekranlarını idarə etmək üçün hazırlanmış rəqəmsal bir dövrdür. Görüntülən çərçivəni təmsil edən Frame Buferdən (VGA Yaddaş) oxuyur və lazım olanları yaradır

Sadə və asan addımlarla PCB dizaynı: 30 addım (şəkillərlə)

Sadə və Asan Adımlarla PCB Dizaynı: SALAM DOSTLAR PCB dizaynını öyrənmək istəyənlər üçün çox faydalı və asan təlimatı başlaya bilərik

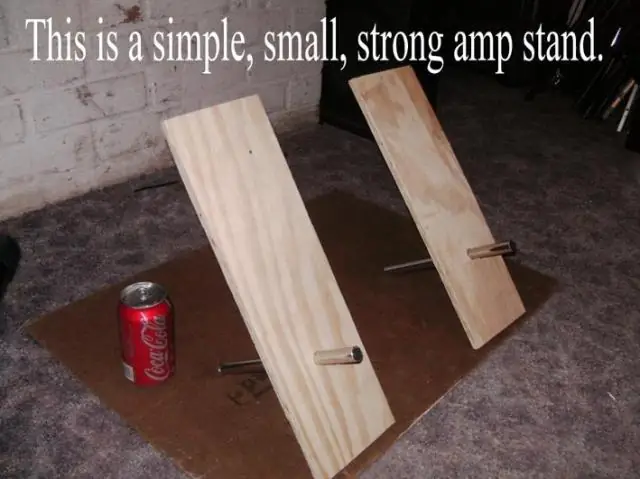

Gitara Amp Tilt Standı - "Afrika Kreslosu" Dizaynı - Sadə, Kiçik, Güclü, Asan, Pulsuz və ya Real Ucuz: 9 Addım

Gitara Amp Tilt Standı - "Afrika Kreslosu" Dizaynı - Sadə, Kiçik, Güclü, Asan, Pulsuz və ya Real Ucuz: Gitara Amp Tilt Standı - Çox Asan - sadə, kiçik, güclü, pulsuz və ya real ucuz. Bütün ölçülü amperlər üçün, hətta ayrı başlıqlı böyük kabinetlər. İstədiyiniz hər hansı bir avadanlıq üçün lazım olan ölçüdə lövhələr və borular hazırlayın