Mündəricat:

- Addım 1: Vivado HLS nədir?

- Addım 2: HLS Video Kitabxanası

- Addım 3: Sintez

- Addım 4: Versiya və ixrac üçün digər məlumatlar

- Addım 5: Vivado IP Kitabxanasına ixrac edin

- Addım 6: Sintez və İxrac Analizi

- Addım 7: Vivadoda IP Kitabxanasının əlavə edilməsi

- Addım 8: Yeniləmə aparın

- Addım 9: Əlavə Məlumatlar və Məlumat

- Addım 10: Çıxış və Giriş

- Addım 11: AXI Qeydiyyat İnterfeysi

- Addım 12: Dataflow Pragma

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:48.

- Son dəyişdirildi 2025-01-23 12:56.

Çox gecikmə əlavə etmədən və ya quraşdırılmış bir sistemdə video üzərində real vaxtda işləmək istəmisinizmi? Bunu etmək üçün bəzən FPGA (Sahə Programlanabilir Gate Dizileri) istifadə olunur; Bununla birlikdə, VHDL və ya Verilog kimi hardware dəqiqləşdirmə dillərində video emal alqoritmləri yazmaq ən yaxşı halda sinir bozucu olur. C ++ mühitində proqramlaşdırmağa və ondan aparat spesifikasiyası dil kodu yaratmağa imkan verən Xilinx vasitəsi Vivado HLS daxil edin.

Tələb olunan proqramlar:

- Vivado HLS

- Vivado

- (AXI qeydlərindən istifadə edirsinizsə) Vivado SDK

(İsteğe bağlı) Xilinx tərəfindən hazırlanmış nümunələri buradan yükləyin:

Xilinx HLS video nümunələri

Addım 1: Vivado HLS nədir?

Vivado HLS, c ++ kodunu FPGA -da tətbiq oluna bilən aparat quruluşlarına çevirmək üçün istifadə olunan bir vasitədir. Bu inkişaf üçün IDE daxildir. Vivado ilə istifadə üçün.

Əlavə edilmiş faylları yükləyin və layihənizi yaradacağınız yerə yaxınlaşdırın. (təsadüfi bir adı varsa, onları "top.cpp" və "top.h" olaraq yenidən adlandırın)

Addım 2: HLS Video Kitabxanası

HLS Video Kitabxanasında bu yazıda istinad dizaynlı sənədlər var: XAPP1167Başqa yaxşı bir qaynaq bu barədə Xilinx Wiki səhifəsidir.

Vivado HLS işə salın.

Yeni bir layihə yaradın.

Əvvəlki addımda yüklədiyiniz faylları götürün və onları mənbə faylları olaraq əlavə edin. (Qeyd: fayllar layihəyə kopyalanmır, əksinə olduğu yerdə qalır)

Sonra üst funksiyanı seçmək üçün Browse düyməsini istifadə edin.

Növbəti səhifədə istifadə etdiyiniz Xilinx hissəsini seçin.

Addım 3: Sintez

Həll => C Sintezini Çalışdırın => Aktiv Həll

~ 227.218 saniyə sonra edilməlidir. (Qeyd: faktiki sintez vaxtınız bir çox faktordan asılı olaraq dəyişəcək)

Addım 4: Versiya və ixrac üçün digər məlumatlar

Versiya nömrələri Vivado ilə qarşılıqlı əlaqə quraraq, bir dizaynda IP -ni yeniləyə bilərsiniz. Kiçik bir versiya dəyişikliyidirsə, əsas versiya dəyişiklikləri əl ilə yeni bloka əlavə etməyi və köhnəsini silməyi tələb edir. yeniləmə IP düyməsinə basaraq tamamilə avtomatik olaraq edilir. IP statusunuzu görmək üçün Vivado tcl konsolunda "report_ip_status" işlədə bilərsiniz.

Versiya nömrələrini və digər məlumatları Həll => Həll Ayarları…

Alternativ olaraq, bu parametrlər ixrac zamanı təyin edilə bilər.

Addım 5: Vivado IP Kitabxanasına ixrac edin

Həll => RTL ixrac edin

Əvvəlki addımda IP kitabxana təfərrüatlarını təyin etməmisinizsə, bunu indi edə bilərsiniz.

Addım 6: Sintez və İxrac Analizi

Bu ekranda ixrac etdiyimiz modulla bağlı statistikanı görə bilərik ki, bu da 10ns (100MHz) saat müddətinə cavab verdiyini və hər bir mənbənin nə qədər istifadə etdiyini göstərir.

Bunun, Sintez Hesabatımızın və Dataflow analizimizin birləşməsi ilə 317338 saat dövrü * 10s saat dövrü * 14 boru kəməri mərhələsi = 0.04442732 saniyə çəkdiyini görə bilərik. Təsvir emalımızın əlavə etdiyi ümumi gecikmənin saniyənin iyirmidən birindən az olduğunu göstərir (hədəflənmiş 100MHz -də).

Addım 7: Vivadoda IP Kitabxanasının əlavə edilməsi

Sintez edilmiş IP blokunuzdan istifadə etmək üçün onu Vivadoya əlavə etməlisiniz.

Vivadoda, IP kataloquna gedərək və "Depo əlavə et …" seçimini sağ tıklayaraq layihənizə bir IP anbarı əlavə edin.

Vivado HLS layihə kataloqunuza gedin və həll kataloqunuzu seçin.

Tapdığı IP haqqında məlumat verməlidir.

Addım 8: Yeniləmə aparın

Bəzən HLS blokunuzu Vivado dizaynına daxil etdikdən sonra dəyişiklik etməlisiniz.

Bunu etmək üçün, dəyişiklikləri edə və daha yüksək bir versiya nömrəsi ilə IP -ni yenidən sintez edə və ixrac edə bilərsiniz (böyük/kiçik versiya nömrəsi dəyişiklikləri ilə bağlı əvvəlki addımdakı detallara baxın).

Yeni versiyanı ixrac etməyi dəyişdirdikdən sonra Vivadodakı IP depolarınızı yeniləyin. Bu ya Vivado IP -nin anbarda dəyişdiyini və ya əl ilə aktiv edildikdə edilə bilər. (Qeyd edək ki, başladıqdan sonra IP depolarınızı yeniləyirsinizsə, lakin ixrac HLS -də tamamlanmadan əvvəl IP müvəqqəti olmayacaq, bitməsini gözləyin və yenidən yeniləyin.)

Bu nöqtədə, diskdə bir IP -nin dəyişdirildiyi və "Seçilmişləri Yükselt" düyməsi ilə yeniləmə imkanı verən bir pəncərə görünməlidir. sonra bu düyməyə basmaq köhnə IP -ni avtomatik olaraq yenisi ilə əvəz edəcək, əks halda daha çox iş tələb oluna bilər.

Addım 9: Əlavə Məlumatlar və Məlumat

Aşağıdakı addımlar HLS sintezinin necə işlədiyi və bununla nə edə biləcəyiniz haqqında daha çox məlumat verir.

HLS sintez edilmiş IP bloku istifadə edən bir layihə nümunəsi üçün bu təlimata baxın.

Addım 10: Çıxış və Giriş

Son IP blokunun çıxışları və girişləri, sintezatorun üst funksiyaya daxil olan və xaricində olan məlumat axınının analizi ilə müəyyən edilir.

VHDL və ya verilogda olduğu kimi, HLS də IP arasındakı əlaqələr haqqında ətraflı məlumat verməyə imkan verir. Bu sətirlər buna misaldır:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE ox portu = video_in bundle = INPUT_STREAM #pragma HLS INTERFACE ox portu = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = HXSEL_setset = 0x14

IP blokunda nümayiş olunan limanların bu direktivlərdən necə təsirləndiyini görə bilərsiniz.

Addım 11: AXI Qeydiyyat İnterfeysi

IP blokunuzdan PS -yə giriş/çıxış əldə etmək üçün bunu etmək üçün yaxşı bir yol AXI interfeysidir.

Bunu dəyərə sonradan daxil olmaq üçün istifadə ediləcək ofsetlər də daxil olmaqla HLS kodunuzda təyin edə bilərsiniz:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x paket = CONTROL_BUS ofset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS ofset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Vivadoda düzgün bir şəkildə bağlandıqdan sonra Vivado SDK -da bu kodu istifadə edərək dəyərlərə daxil ola bilərsiniz:

#"parametre.h" daxil edin

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Bu, x -də 42 və y -də 0xdeadbeef ilə nəticələnməyinizə səbəb olacaq

Addım 12: Dataflow Pragma

#Pragma DATAFLOW daxilində kodun tətbiq edilməsi normal C ++ dan dəyişir. Kod, bütün təlimatların hər zaman məlumatların fərqli hissələrində çalışması üçün boru kəməridir (Bir fabrikdə montaj xətti kimi düşünün, hər stansiya bir funksiyanı yerinə yetirərək növbəti stansiyaya ötürülür)

şəkildən direktivlərin hər birinin olduğunu görə bilərsiniz

Normal dəyişən kimi görünməsinə baxmayaraq, img obyektləri əslində əmrlər arasında kiçik tamponlar kimi tətbiq olunur. Şəkli bir funksiyaya giriş olaraq istifadə etmək onu "istehlak edir" və artıq istifadəyə yaramır. (Buna görə də təkrarlanan əmrlərə ehtiyac var)

Tövsiyə:

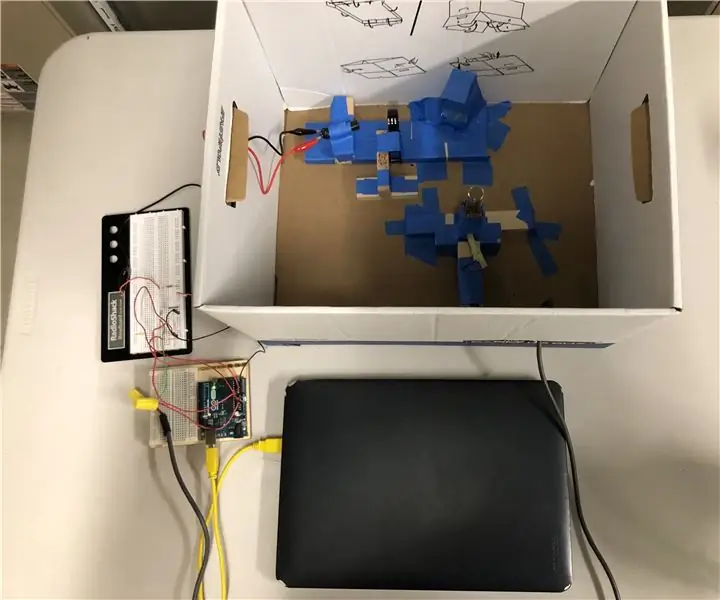

Yosun təcrübələri üçün evdə hazırlanan Jenga Blok Spektrofotometri: 15 addım

Yosun Təcrübələri üçün Ev Yapımı Jenga Blok Spektrofotometri: Yosunlar fotosintetik protistlərdir və su qida zəncirlərində kritik orqanizmlərdir. Yaz və yaz aylarında, bu və digər mikroorqanizmlər təbii su ehtiyatlarını çoxalda və basdıra bilər, nəticədə oksigen tükənir

Səs əyilmə sintezi: 14 addım (şəkillərlə)

Səs bükülmə sintezi: Daha əvvəl bir neçə səs bükmə maşını qurmuşam ("ibles" ə aşağıdakı bağlantılara baxın). Bu dəfə sizə həqiqətən oynamaq üçün yeni bir səs çeşidi verən bir reverb və amp modulu əlavə etdim. Üstəlik, səs yazıcı modulu

Retro nitq sintezi. Bölmə: 12 IoT, Ev Avtomatlaşdırması: 12 Addım (Şəkillərlə)

Retro nitq sintezi. Hissə: 12 IoT, Ev Avtomatlaşdırması: Bu məqalə, ev avtomatlaşdırılması ilə bağlı bir sıra 12 -ci məqalədir

Vivado Simulyasiyasından necə istifadə olunur: 6 addım

Vivado Simulyasiyasından Necə İstifadə Edilir: Bu simulyasiya layihəsini onlayn dərs üçün etmişəm. Layihə Verilog tərəfindən yazılmışdır. Vivadoda simulyasiya vasitəsi ilə, əvvəllər yaradılmış stop -saat layihəsindən enable_sr (aktiv rəqəm) dalğa şəklini görüntüləmək üçün istifadə edəcəyik. Əlavə olaraq, bizi

Kompüterinizdə analoq səs sintezi: 10 addım (şəkillərlə birlikdə)

Kompüterinizdə Analog Səs Sintezi: Köhnə analoq sintezatorların səsi kimi? Öz vaxtınızda, öz yerinizdə, istədiyiniz qədər PULSUZ oynamaq istəyirsiniz? Ən çılğın Moog xəyallarınızın gerçəkləşdiyi yer budur. Elektron səs yazma sənətçisi və ya jus ola bilərsiniz