Mündəricat:

- Addım 1: Mənbə əlavə edin və "Simulyasiya mənbələri əlavə et və ya yaradın" seçin

- Addım 2: Enable_sr_tb adlı bir fayl yaradın

- Addım 3: Testbench Faylını yaradın

- Addım 4: Enable_sr_tb -ni Simulyasiya Altında Üst Səviyyə olaraq təyin edin

- Addım 5: Sintez və Davranış Simulyasiyasını Çalışdırın

- Addım 6: Simulyasiya nəticəsini qiymətləndirin

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:47.

- Son dəyişdirildi 2025-01-23 12:54.

Bu simulyasiya layihəsini onlayn dərs üçün etdim. Layihə Verilog tərəfindən yazılmışdır. Vivadoda simulyasiya vasitəsi ilə, əvvəllər yaradılmış stop -saat layihəsindəki enable_sr (aktiv rəqəm) dalğa formasını görüntüləmək üçün istifadə edəcəyik. Əlavə olaraq, dizaynda etdiyimiz səhvləri göstərmək üçün sistem tapşırığından istifadə edəcəyik.

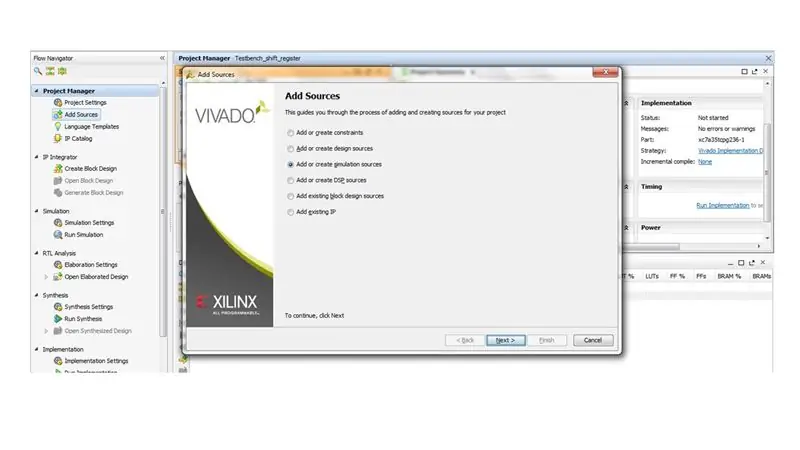

Addım 1: Mənbə əlavə edin və "Simulyasiya mənbələri əlavə et və ya yaradın" seçin

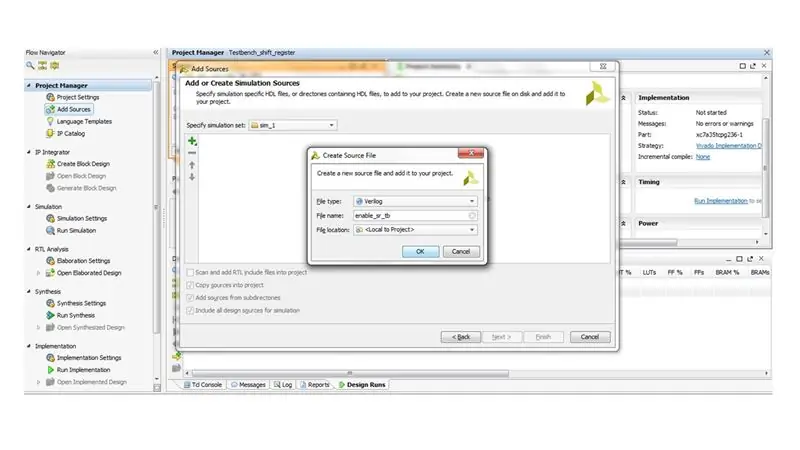

Addım 2: Enable_sr_tb adlı bir fayl yaradın

Addım 3: Testbench Faylını yaradın

1. Enable_sr modulunu stop watch layihəsindən idxal edin. Simulyasiya etmək istədiyimiz sənəd budur

2. Enable_sr_tb () testbench modulu yaradın;

3. enable_sr () modulunun giriş və çıxışlarını daxil edin. Unutmayın ki, enable_sr üçün girişlər indi qeyd tipindədir, nəticələr isə net tipə çevrilir.

4. Enable_sr olan sınaqdan keçirilmiş vahidi (uut) işə salın

5. (T) dövrü 20 ns olan saatı yaradın

6. Səhv yoxlama sistemi yaratmaq üçün şərti ifadəni istifadə edin. Bu nümunədə, birdən çox rəqəmin aktiv olub olmadığını yoxlamaq istəyirik.

Qeyd: Orijinal enable_sr () faylında, nümunəni 4'b0011 olaraq başlamalıyıq ki, səhv yaratmaq üçün iki rəqəm aktiv olsun

7. Səhv göstərmək üçün $ display sistem tapşırığını istifadə edin

8. Simulyasiyanı 400ns vaxtında başa çatdırmaq üçün $ finish sistem tapşırığını istifadə edin

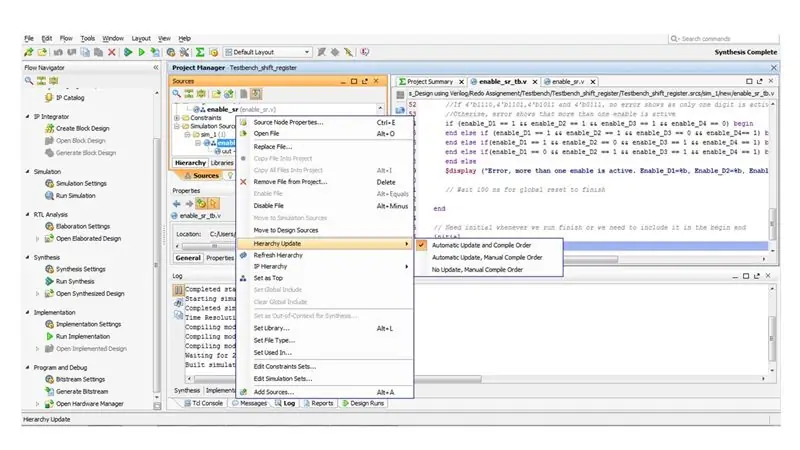

Addım 4: Enable_sr_tb -ni Simulyasiya Altında Üst Səviyyə olaraq təyin edin

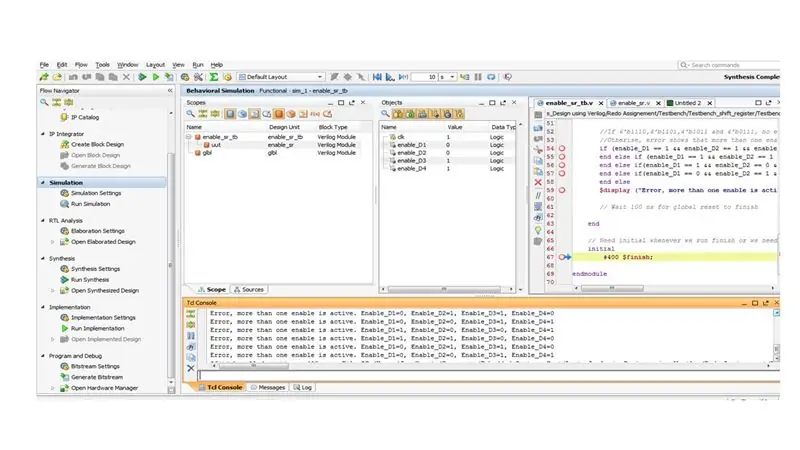

Addım 5: Sintez və Davranış Simulyasiyasını Çalışdırın

- Davranış simulyasiyasına başlamazdan əvvəl testbench faylında və test faylının altındakı vahiddə sintaksis səhvlərinin olmadığından əmin olmaq üçün sintezi işə salın.

- Davranış simulyasiyasını işə salın

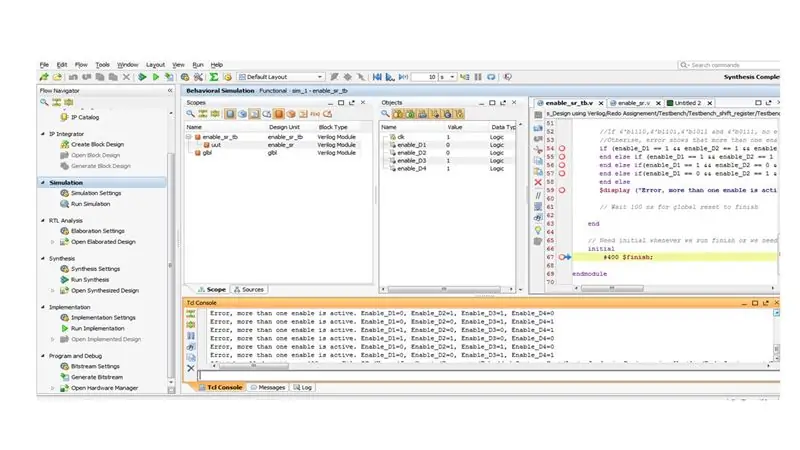

Addım 6: Simulyasiya nəticəsini qiymətləndirin

Simulyasiya pəncərələrini görəcəksiniz. Fərqli panellərdən ibarətdir.

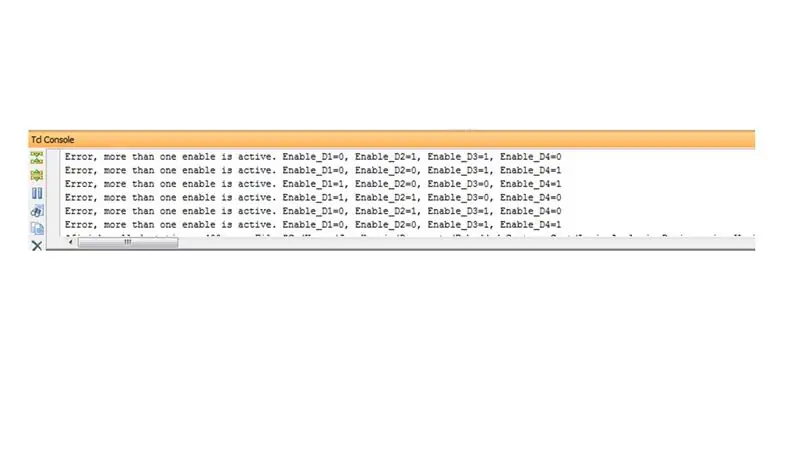

Konsol panelində səhv mesajını görəcəksiniz. Bu simulyasiya dövründə birdən çox rəqəmin aktiv olduğunu göstərir.

Dalğa formasını da əhatə dairəsində görə bilərsiniz

Layihə faylı əlavə olunur.

Tövsiyə:

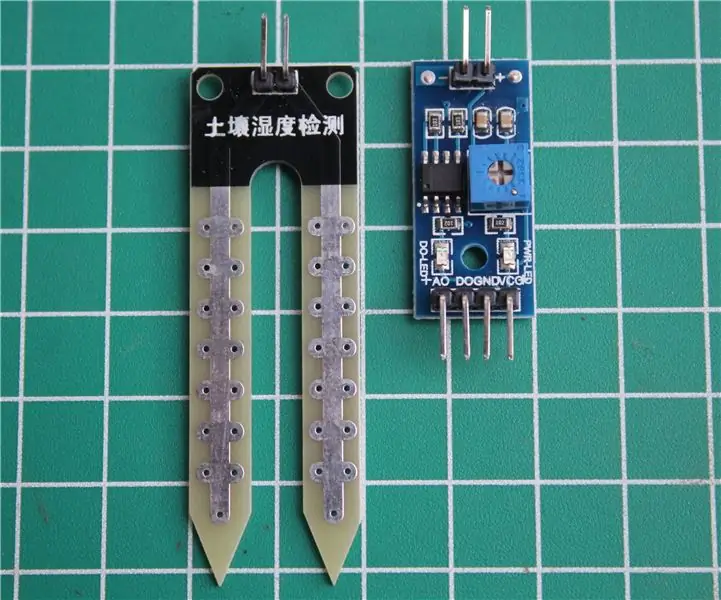

Arduino istifadə edərək Torpaq Nəm Sensorundan necə istifadə olunur: 4 addım

Torpaq Nəm Sensorunu Arduino istifadə edərək necə istifadə etmək olar: Torpaq Nəm sensoru, torpağın nəmini ölçmək üçün istifadə edilə bilən bir sensordur. Ağıllı əkinçilik layihələrinin, Suvarma nəzarətçiləri layihələrinin və ya IoT Kənd Təsərrüfatı layihələrinin prototiplərini hazırlamaq üçün uyğundur. Bu sensorun 2 probu var. Mənə öyrəşmiş

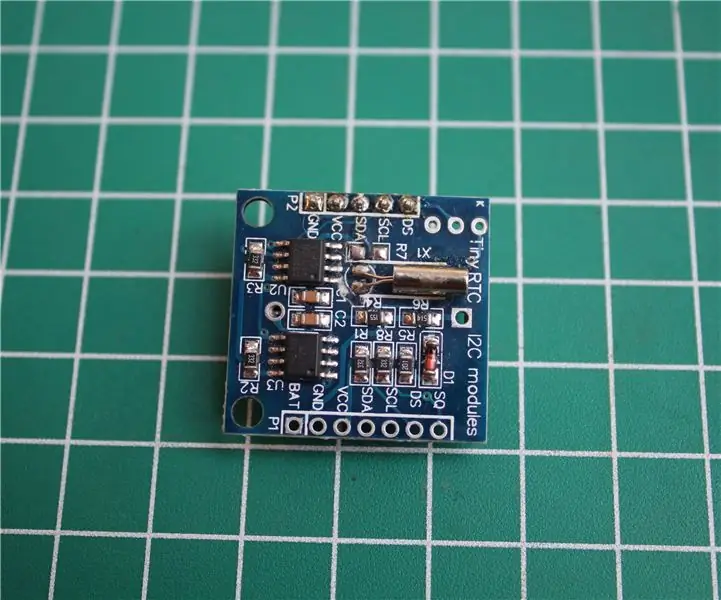

DS1307 Arduino istifadə edərək necə istifadə olunur: 7 addım

DS1307 Arduino istifadə edərək necə istifadə olunur: DS1307, Real Zamanlı Saat IC (RTC). Bu IC vaxt məlumatlarını təmin etmək üçün istifadə olunur. Ayrılan vaxt Saniyələr, Dəqiqələr, Saatlar, Günlər, Tarix, Ay və İldən başlayır.Bu IC, Crystal və 3.6V Batareyalar kimi əlavə xarici komponentlər tələb edir. Kristal

Rotary Encoder: necə işləyir və Arduino ilə necə istifadə olunur: 7 addım

Rotary Encoder: Arduino ilə necə işləyir və necə istifadə olunur: Bu və digər möhtəşəm dərsləri ElectroPeak -in rəsmi saytında oxuya bilərsinizBaxış Bu dərsdə, fırlanan kodlayıcıdan necə istifadə edəcəyinizi öyrənəcəksiniz. Əvvəlcə fırlanma kodlayıcısı haqqında bəzi məlumatlar görəcəksiniz və sonra necə edəcəyinizi öyrənəcəksiniz

Blynk istifadə edərək Wemos ESP-Wroom-02 D1 Mini WiFi Modulu ESP8266 + 18650-dən necə istifadə olunur: 10 addım

Blynk istifadə edərək Wemos ESP-Wroom-02 D1 Mini WiFi Modulu ESP8266 + 18650 Necə İstifadə olunur: Xüsusiyyətlər: nodemcu 18650 şarj sistemi inteqrasiyasına uyğundur Göstərici LED (yaşıl tam qırmızı deməkdir, şarj deməkdir) Şarj edilərkən Şəbəkə idarəetmə enerji təchizatı SMT bağlayıcı yuxu rejimi üçün istifadə edilə bilər · 1 əlavə

Blynk istifadə edərək Arduino WeMos D1 WiFi UNO ESP8266 IOT IDE uyğun lövhədən necə istifadə olunur: 10 addım

Blynk istifadə edərək Arduino WeMos D1 WiFi UNO ESP8266 IOT IDE Uyğun lövhədən necə istifadə olunur: Arduino WeMos D1 WiFi UNO ESP8266 IOT IDE Uyğun lövhə Təsviri: WiFi ESP8266 İnkişaf Etmə Paneli WEMOS D1. WEMOS D1, ESP8266 12E -ə əsaslanan WIFI inkişaf lövhəsidir. İşləmə, NODEMCU -ya bənzəyir, ancaq hardware quraşdırılmışdır