Mündəricat:

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:46.

- Son dəyişdirildi 2025-01-23 12:54.

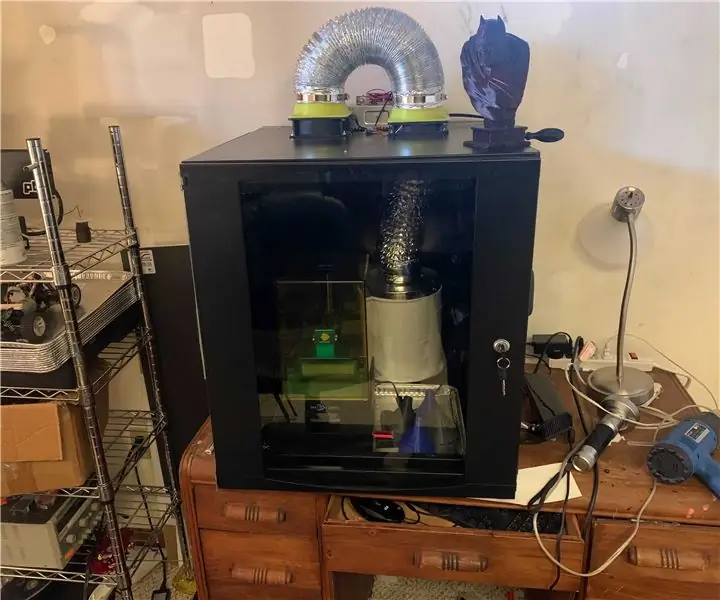

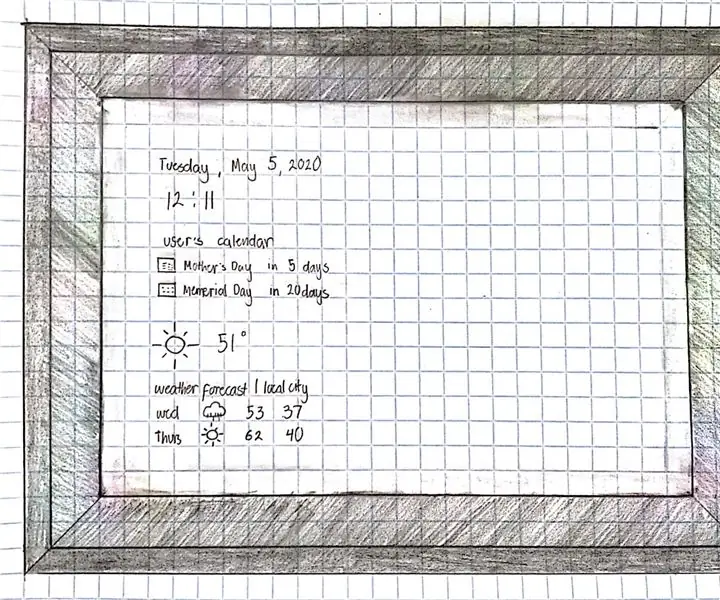

Bu layihənin məqsədi Smart Mirror -un görüntü görüntü funksiyasını yaratmaqdır. Güzgü, proqnozları (günəşli, qismən günəşli, buludlu, küləkli, yağışlı, ildırımlı və qarlı) və -9999 ° ilə 9999 ° arasındakı temperatur dəyərlərini göstərə bilir. Proqnoz və temperatur dəyərləri, bir hava API -dən təhlil edilməsini təqlid etmək üçün sərt kodlanır.

Layihə, FreeRTOS ilə işləyən bir Zynq-Zybo-7000 lövhəsindən istifadə edir və avadanlıqların dizaynı və proqramlaşdırılması üçün Vivado 2018.2-dən istifadə edir.

Parçalar:

Zynq-Zybo-7000 (FreeRTOS ilə)

19 LCD (640x480)

VGA kabeli

12 "x 18" akril güzgü

Addım 1: Vivado'yu konfiqurasiya edin

Xilinx -dən Vivado 2018.2 -ni yükləyin və Webpack lisenziyasından istifadə edin. Vivadonu və "Yeni Layihə Yarat" ı işə salın və ona bir ad verin. Sonra "RTL Layihəsi" ni seçin və "Hazırda mənbələri göstərməyin" işarəsini qoyun. Bir hissə seçərkən "xc7z010clg400-1" seçin və növbəti səhifədə "Bitir" düyməsini basın.

Addım 2: VGA Sürücü IP -nin qablaşdırılması

Vga_driver.sv faylını Dizayn Mənbələrinə əlavə edin. Sonra "Alətlər" düyməsini basın və "Yeni IP Yarat və Paketlə" seçin. "Cari layihənizi paketləyin" seçin. Sonra bir IP yeri seçin və ".xci fayllarını daxil edin." Açılan pəncərədə "OK" düyməsini və sonra "Finish" düyməsini basın.

"Qablaşdırma Adımları" nda "Baxış və Paketləmə" bölməsinə gedin və "Paket IP" ni seçin.

İndi vga_driver bir IP blok olaraq mövcud olmalıdır.

Addım 3: Zynq IP

"IP İnteqratoru" bölməsinin altında "Blok Dizaynı Yarat" ı seçin. "ZYNQ7 İşləmə Sistemi" ni əlavə edin və bloka iki dəfə vurun. "Import XPS Settings" düyməsini basın və ZYBO_zynq_def.xml faylını yükləyin.

Sonra, "PS-PL Konfiqurasiyası" altında "AXI Qeyri Təhlükəsiz Təhlükəsizlik" açılır siyahısını açın və "M AXI GP0 interfeysi" ni yoxlayın.

Sonra, "MIO Konfiqurasiyası" altında "Tətbiq Prosessor Birimi" açılır menyusunu açın və "Taymer 0" və "Gözətçi" ni yoxlayın.

Nəhayət, "Saat Konfiqurasiyası" altında "PL Fabric Clocks" açılır siyahısını açın və "FCLK_CLK0" və 100 MHz -də yoxlayın.

Addım 4: GPIO IP

Blok Dizaynına iki GPIO bloku əlavə edin. GPIO -lar piksel ünvanını və piksellərin RGB komponentlərini idarə etmək üçün istifadə ediləcək. Yuxarıdakı şəkillərdə göstərildiyi kimi blokları konfiqurasiya edin. Hər iki bloku əlavə edib konfiqurasiya etdikdən sonra "Bağlantı Otomasyonunu Çalıştır" düyməsini basın.

GPIO 0 - Kanal 1 piksel ünvanını və Kanal 2 qırmızı rəngi idarə edir.

GPIO 1 - Kanal 1 yaşıl rəngə, Kanal 2 mavi rəngə nəzarət edir.

Addım 5: Yaddaşı bloklayın

Blok Dizaynına Block Memory Generator IP əlavə edin və yuxarıda göstərildiyi kimi konfiqurasiya edin. Piksel rəngləri VGA sürücüsü tərəfindən oxunan yaddaş ünvanlarına yazılır. Ünvan xətti, istifadə olunan piksellərin miqdarına uyğun olmalıdır, buna görə 16 bit olmalıdır. 16 rəngli bit olduğu üçün məlumatlar da 16 bitdir. Hər hansı bir təsdiq bitini oxumaq bizi maraqlandırmır.

Addım 6: Digər IP

Əlavə edilmiş pdf tamamlanmış Blok Dizaynını göstərir. İtkin IP əlavə edin və əlaqələri tamamlayın. VGA rəngli çıxışları və şaquli və üfüqi sinxronizasiya çıxışları üçün də "Xaricilər yaradın".

xlconcat_0 - Blok RAM -a daxil olan 16 bitlik RGB siqnalı yaratmaq üçün fərdi rəngləri birləşdirir.

xlconcat_1 - VGA sürücüsünün sütun və satır siqnallarını birləşdirir və Blok RAM -in B Portuna verilir. Bu, VGA sürücüsünə piksel rəng dəyərlərini oxumağa imkan verir.

VDD - Daimi YÜK, Blok RAM -ın yazma imkanlarına bağlıdır, buna görə hər zaman buna haqq qazana bilərik.

xlslice_0, 1, 2 - Dilimlər, RGB siqnalını VGA sürücüsünə ötürülə bilən fərdi R, G və B siqnallarına bölmək üçün istifadə olunur.

Blok Dizaynı tamamlandıqdan sonra bir HDL sarğı yaradın və məhdudiyyətlər faylını əlavə edin.

*Blok Dizayn benlin1994 tərəfindən yazılmış dərslikdən irəli gəlir*

Addım 7: SDK

Bu Blok Dizaynını işlədən kod aşağıda verilmişdir. Init.c, rəsmlə işləyən funksiyaları (proqnozlar, ədədlər, dərəcə işarəsi və s.) Ehtiva edir. Main.c -dəki əsas döngə, lövhə proqramlaşdırıldıqda işləyən şeydir. Bu döngə proqnoz və temperatur dəyərlərini təyin edir və sonra init.c. -də çəkmə funksiyalarını çağırır. Hal -hazırda yeddi proqnozu araşdırır və bir -birinin ardınca göstərir. Hər bir görüntünü görə bilmək üçün 239 -cu sətirdə bir fasilə nöqtəsi əlavə etməyiniz məsləhətdir. Kod şərh olunur və sizə daha çox məlumat verəcəkdir.

Addım 8: Nəticə

Mövcud layihəni yaxşılaşdırmaq üçün COE faylları şəklində əvvəlcədən yüklənmiş proqnoz şəkillərini Blok Yaddaş generatorlarına yükləyə bilərsiniz. Beləliklə, C kodundakı kimi proqnozları əl ilə çəkmək əvəzinə, şəkilləri oxumaq olardı. Bunu etməyə çalışdıq, amma işə yaramadı. Piksel dəyərlərini oxuya və çıxara bildik, ancaq RAM -a yüklədiyimizə bənzəməyən qarışıq şəkillər yaratdı. Blok Yaddaş Generatoru məlumat cədvəlini oxumaq üçün faydalıdır.

Layihə, İnternet bağlantısı baxımından əskik olduğu üçün yarı Smart Güzgüdür. Bunu əlavə etsəniz, tam bir Smart Mirror əldə edərsiniz.

Tövsiyə:

Sonsuzluq güzgü saatı hazırlayın: 15 addım (şəkillərlə)

Sonsuzluq Güzgü Saatı yaradın: Əvvəlki bir layihədə sonsuzluq güzgüsü qurmuşdum, burada əsas məqsədim onu saata çevirmək idi. (Rəngarəng Sonsuzluq Güzgüsü düzəldin) Bunu qurduqdan sonra bunu davam etdirmədim, çünki sərin görünsə də, bir neçə şey var idi

C.Q: DIY Ağıllı Güzgü: 5 addım

C.Q: DIY Ağıllı Güzgü: Biz Katrina Concepcion və Adil Qaiser, WBASD STEM Akademiyasının ikinci kursunda oxuyuruq. Bu ilin ən yaxşı mükafatı üçün əməkdaşlıq edəcəyimiz və edəcəyimiz layihədir. Bu layihəni etmək qərarına gəldiyimiz zaman " ən çox nə olacağını düşündük

LCD və IR Sensorlu Sonsuzluq Güzgü: 5 addım

LCD və İQ Sensorlu Sonsuzluq Güzgüsü: Bu layihə sizə Sonsuzluq Güzgüsünün necə yaradılacağını göstərəcək. Əsas konsepsiya, güzgüdə olan LED -lərin arxa güzgüdən ön güzgüyə doğru sıçrayan bir işıq yaratmasıdır ki, içəridən görə biləcəyimiz bir qədər işıq çıxır

2 tərəfli, masa üstü sonsuz güzgü hazırlayın: 14 addım (şəkillərlə)

2 tərəfli, masa üstü sonsuz güzgü hazırlayın: gördüyüm sonsuzluq güzgülərinin çoxu bir tərəflidir, amma bir az fərqli qurmaq istədim. Bu, iki tərəfli olacaq və masaüstündə və ya rəfdə göstərilə biləcək şəkildə hazırlanacaq. Hazırlanması asan, çox gözəl bir layihədir

Raspberry Pi Ekranı və Toxunma Ekranı: 4 Addım

Raspberry Pi Ekranı və Toxunma Ekranı Döndür: Bu, Buster Raspbian əməliyyat sistemi ilə işləyən hər hansı bir Raspberry Pi üçün ekranı və toxunma girişini necə döndərəcəyinizi göstərmək üçün əsas bir təlimatdır, amma Jessie -dən bəri bu üsuldan istifadə edirəm. Burada istifadə olunan şəkillər bir Raspberry Pi -dən