Mündəricat:

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:46.

- Son dəyişdirildi 2025-01-23 12:54.

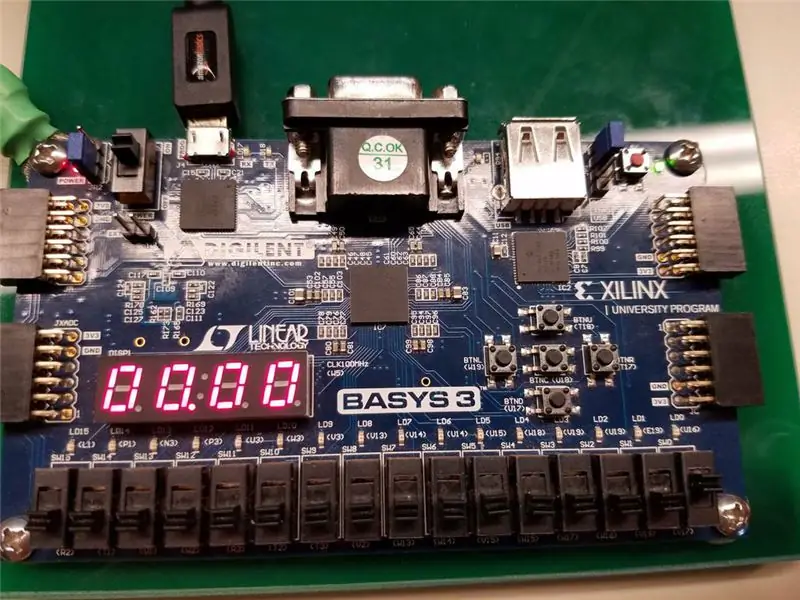

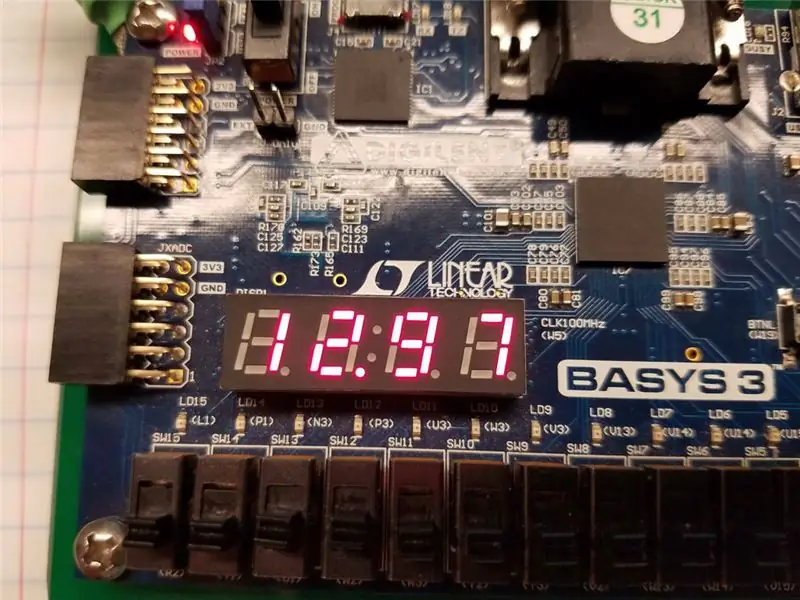

Əsas VHDL və Basys 3 lövhəsini istifadə edərək saniyəölçən qurmağın təlimatçısına xoş gəlmisiniz. Layihəmizi sizinlə bölüşməkdən məmnunuq! Bu, Payız 2016 -da Cal Poly, SLO -da CPE 133 (Rəqəmsal Dizayn) kursu üçün son bir layihə idi. Qurduğumuz layihə vaxtı başlayan, sıfırlayan və durduran sadə bir saniyəölçəndir. Giriş olaraq Basys3 lövhəsindəki üç düyməni alır və vaxt lövhənin dörd rəqəmli yeddi seqmentli ekranında göstərilir. Keçən vaxt bir saniyədə göstərilir: saniyə saniyə formatı. Anakartın sistem saatını keçən vaxtı izləmək üçün giriş olaraq istifadə edir və vaxtı yeddi seqmentli ekranın dörd rəqəminə çıxarır.

Addım 1: Materiallar

Bu layihə üçün sizə lazım olacaq materiallar:

- Xilinx -dən Vivado Design Suite WebPack quraşdırılmış 1 kompüter (2016.2 versiyasına üstünlük verin)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA kartı

- 1 USB port kabeli

Addım 2: Giriş və Çıxışların Ayarlanması

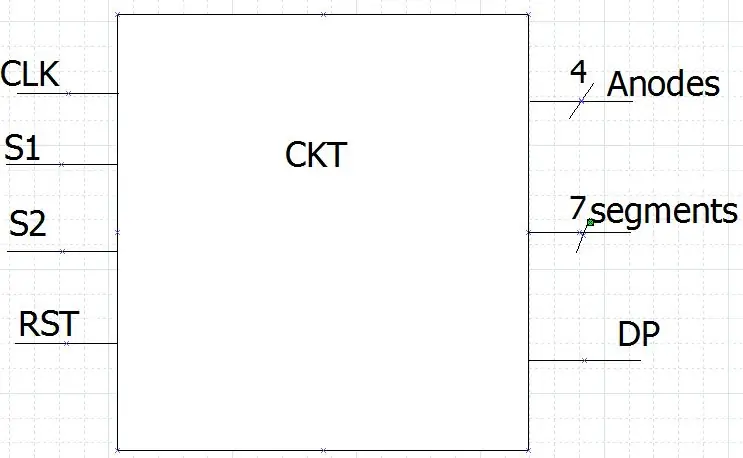

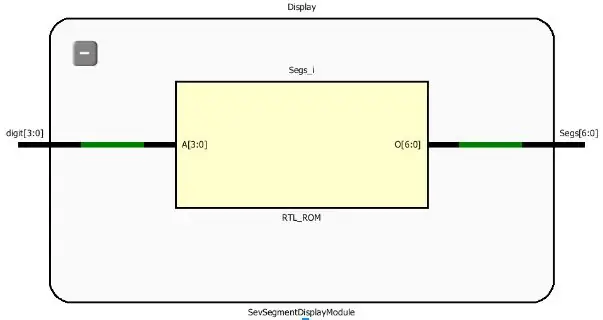

Yuxarıdakı şəkil əsas saniyəölçən modulunun ən yüksək səviyyəli blok diaqramını göstərir. Saniyəölçən "CLK" (saat), "S1" (başlanğıc düyməsi), "S2" (fasilə düyməsi) və "RST" (sıfırlama) girişlərini alır və 4 bit çıxışlı "Anodlar", 7 bit "seqment" və tək bitli "DP" (ondalık nöqtəsi) çıxışı. "S1" girişi yüksək olduqda, saniyəölçən vaxt saymağa başlayır. "S2" aşağı olduqda, saniyəölçən vaxtı dayandırır. "RST" yüksək olduqda, saniyəölçən dayanır və vaxtı sıfırlayır. Dövrə daxilində dörd alt modul var: saat bölücü, rəqəm sayacı, yeddi seqmentli ekran sürücüsü və yeddi seqmentli ekran kodlayıcısı. Saniyəölçənin əsas modulu bütün alt modulları birləşdirir və giriş və çıxışlara bağlayır.

Addım 3: Saatların hazırlanması

Saat bölücü modulu sistem saatını götürür və sistem saatından daha böyük olmayan istənilən sürətdə bir saat yaratmaq üçün bölücü girişdən istifadə edir. Saniyəölçən iki fərqli saat modulundan istifadə edir: biri 500 Hz, digəri isə 100 Hz. Saat bölücünün sxemi yuxarıdakı şəkildə göstərilmişdir. Saat bölücü tək bitli "CLK", 32 bitlik "Bölücü" və tək bitli "CLKOUT" girişini alır. "CLK" sistem saatıdır və "CLKOUT" yaranan saatdır. Modul, say bölücünün dəyərinə çatdıqda "CLKTOG" siqnalını dəyişdirən NOT qapısını da ehtiva edir.

Addım 4: Ona qədər sayın

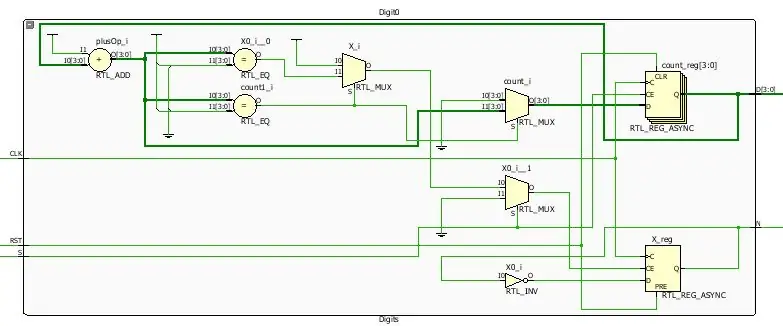

Rəqəm sayacı hər bir rəqəmi 0-dan 10-a qədər sayır və sayın 10-a çatdıqda bu rəqəmin sönməsi üçün başqa bir rəqəmin işləməsi üçün başqa bir saat yaradır. Modul 3 tək bitli "S", "RST" və "CLK" qəbul edir. "və bir bitlik" N "və 4 bitlik" D "çıxışı ilə nəticələnir. "S" girişi, girişdəki aktivdir. Saat "S" yüksək olduqda açılır və "S" aşağı olduqda sönür. "RST" sıfırlama girişidir, buna görə "RST" yüksək olduqda saat sıfırlanır. "CLK" rəqəm sayacı üçün saat girişidir. "N", növbəti rəqəm üçün giriş saatı olan saat çıxışıdır. "D" çıxışı sayğacın yerləşdiyi rəqəmin ikili dəyərini təqdim edir.

Addım 5: Nömrələrin göstərilməsi

Yeddi seqmentli ekran kodlayıcısı, yeddi seqmentli ekran sürücüsü modulundan alınan ikili nömrəni kodlaşdıracaq və ekranın hər seqmenti üçün '1' və ya '0' dəyərləri olaraq şərh ediləcək bit axınına çevirəcək. İkili nömrə modul tərəfindən 4 bitlik "rəqəm" olaraq qəbul edilir və 7 bitlik "seqmentlər" ilə nəticələnir. Modul, 0-dan 9-a qədər hər bir mümkün giriş dəyəri üçün xüsusi 7-bit axını təyin edən tək bir iş proses blokundan ibarətdir. Yeddi-bit axınlarındakı hər bit ekrandakı rəqəmlərin yeddi seqmentindən birini təmsil edir. Akımdakı seqmentlərin sırası "abcdefg" dir və "0" verilən rəqəm üçün yanan seqmentləri təmsil edir.

Addım 6: Saniyəölçəni necə göstərmək olar

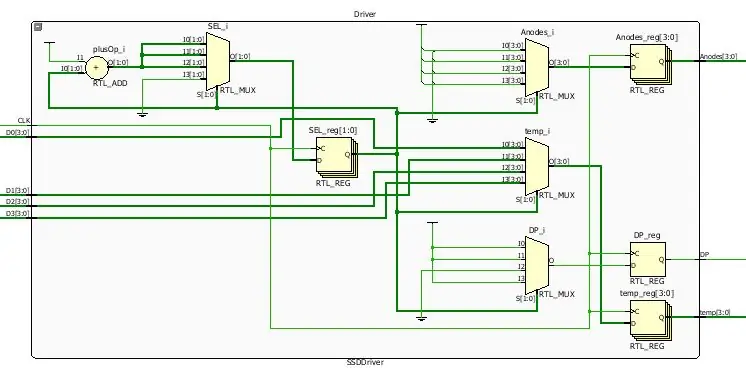

Yeddi seqmentli ekran sürücüsü modulunda, hər biri göstəriləcək dörd rəqəmi təmsil edən dörd "bit D0", "D1", "D2" və "D3" 4 giriş var. Giriş "CLK" sistemin saat girişidir. Tək bitli çıxış "DP", yeddi seqmentli ekranda ondalık nöqtəni təmsil edir. 4-bit çıxışı "Anodlar", yeddi seqmentli ekranda hansı rəqəmin göstəriləcəyini təyin edir və 4 bitlik "temp" 2 bitlik nəzarət girişinin "SEL" vəziyyətindən asılıdır. Modul "SEL" nəzarət girişi və üç çıxış üçün 4 multiplekserdən istifadə edir; "Anodlar", "temp" və "DP".

Addım 7: Hamısını bir araya gətirin

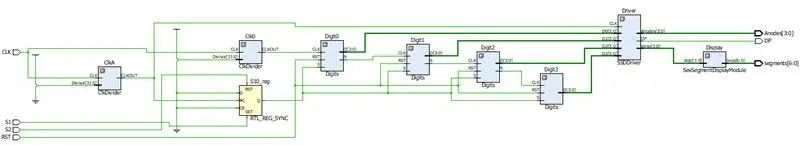

Başlanğıc və fasilə düymələrini yaratmaq üçün 500 Hz saatında işləyən 'if' proses bloku istifadə olunur. Sonra hər bir submodulun komponentlərini elan edərək və müxtəlif siqnallardan istifadə edərək bütün alt modulları saniyəölçən əsas modulunda birləşdirin. Rəqəmli submodullar, əvvəlki rəqəmin alt modulunun saat çıxışını, 100Hz -də birincisini alır. Rəqəmli alt modulların "D" çıxışları daha sonra yeddi seqmentli ekran sürücüsü modulunun "D" girişinə çevrilir. Və nəhayət, yeddi seqmentli ekran sürücüsü modulunun "temp" çıxışı yeddi seqment kodlayıcı modulunun "temp" girişinə çevrilir.

Addım 8: Məhdudiyyətlər

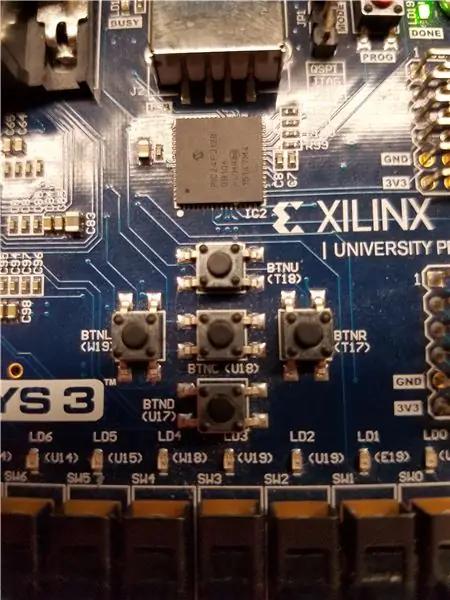

"RST", "S1" və "S2" girişləri üçün 3 düyməni (W19, T17 və U18) istifadə edin. W19 sıfırlama düyməsidir, T17 başlanğıc düyməsidir (S1) və U18 fasilə düyməsidir (S2). W5 portundan istifadə edərək saat girişi üçün bir məhdudiyyət də tələb olunur. Həm də bu xətti saat məhdudiyyətinə əlavə etməyi unutmayın:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

Anodları və seqmentləri lövhəyə bağlayın ki, saniyəölçən məhdudiyyətlər sənədində göründüyü kimi yeddi seqmentli ekranda göstərilsin.

Addım 9: Test

Cihazınızın üç düymə ilə oynayaraq işlədiyinə əmin olun: kodunuzla əlaqədar hər hansı bir problem tapmaq üçün onları mümkün olan qaydada basıb saxlayın.

Tövsiyə:

Notepad istifadə edərək əsas bir veb saytı necə etmək olar: 4 addım

Notepad istifadə edərək əsas bir veb saytı necə qurmaq olar: Hər kəs "əsas bir yazı proqramından bir veb saytı necə düzəldə bilərəm?" Sualına varmı? Aydındır ki, xüsusi olaraq deyil … Hər halda, burada sizə BASIC -in necə hazırlanacağını göstərəcəyəm. yalnız notepad istifadə edərək veb sayt

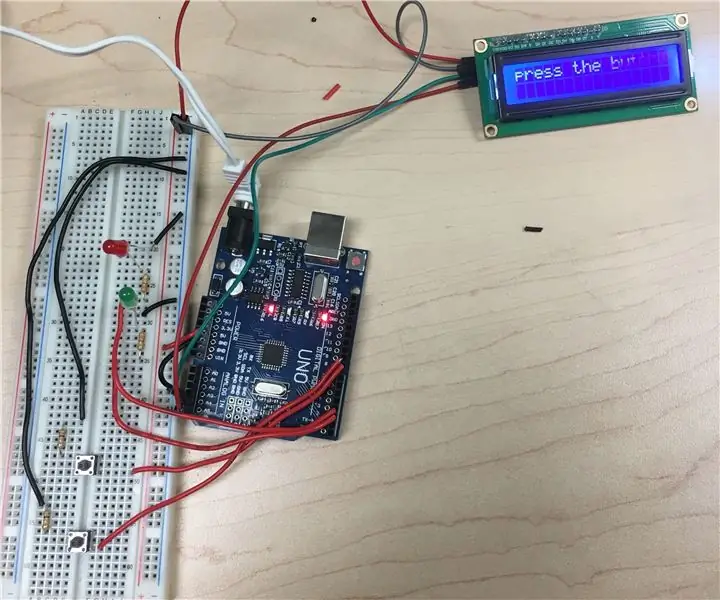

I2C LCD istifadə edərək Arduino Saniyəölçən: 5 addım

I2C LCD istifadə edərək Arduino Saniyəölçən: Bu layihədə sizə LCD displey və Arduino interaktiv bir saniyəölçən kimi istifadə etməyi öyrədəcəyəm. Layihəniz verilən kodla tamamlandıqda yuxarıdakı fotoşəkilə bənzəməlidir. Haradan başlayacağınızı öyrənmək üçün növbəti addıma keçin

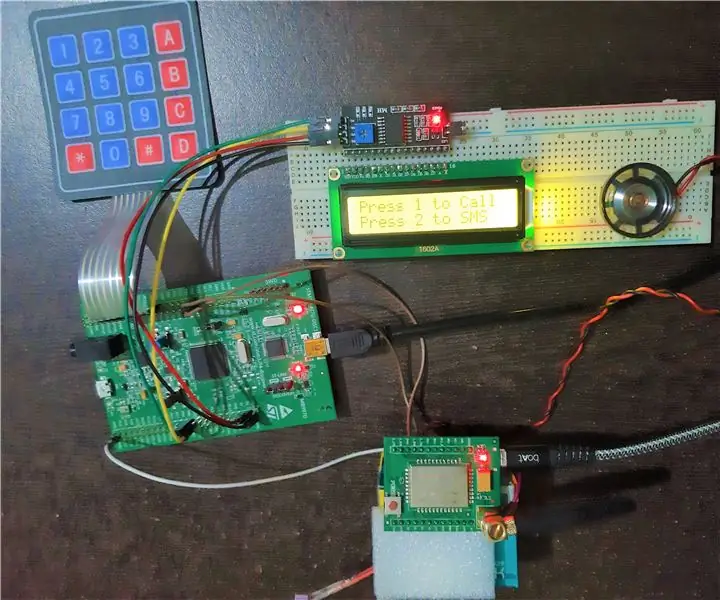

STM32F407 Discovery Kit və GSM A6 Modulundan istifadə edərək Əsas Cib Telefonu: 14 Addım (Şəkillərlə)

STM32F407 Discovery Kit və GSM A6 Modulundan İstifadə Edilən Əsas Cib Telefonu: Heç sərin bir quraşdırılmış layihə yaratmaq istəmisinizmi? Əgər belədirsə, ən populyar və hər kəsin ən çox sevdiyi gadget'lardan birini, yəni Mobil Telefonu qurmağa necə !!! Bu Təlimat kitabında, STM -dən istifadə edərək əsas bir cib telefonu qurmaq üçün sizə yol göstərəcəyəm

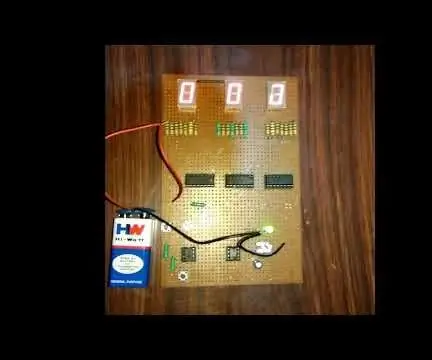

555: 3 addımlardan istifadə edərək rəqəmsal saniyəölçən necə edilir

555 -dən istifadə edərək rəqəmsal saniyəölçən necə edilir: 3 yeddi seqmentli LED displeydən istifadə edərək sadə bir saniyəölçən düzəltdim ki, onlardan birincisi saniyələrin 10 -cu hissəsini digərində 10 saniyəlik saniyələr üçün ikinci, üçüncüsünü isə 555 taymerdən istifadə etdim. 1 saniyədə siqnal verir

Əsas Damğa 2 (bs2) və Charlieplexing istifadə edərək 5x4 LED Ekran Matrixi: 7 Addım

Basic Stamp 2 (bs2) və Charlieplexing istifadə edərək 5x4 LED Ekran Matrixi: Əsas Stamp 2 və ətrafda oturan bəzi əlavə LEDlər varmı? Niyə charlieplexing konsepsiyası ilə oynamırsınız və yalnız 5 pin istifadə edərək bir çıxış yaratmırsınız. Bunun üçün BS2e istifadə edəcəyəm, ancaq BS2 ailəsinin hər hansı bir üzvü işləməlidir