Mündəricat:

- Addım 1: Verici üçün Zynq Proqramlaşdırıla bilən Məntiqi konfiqurasiya edin

- Addım 2: Alıcı üçün Zynq Proqramlaşdırıla bilən Məntiqi konfiqurasiya edin

- Addım 3: VDMA Sürücüsünü qurun

- Addım 4: Nanorouter Şəbəkəsini qurun

- Addım 5: Ethernet vasitəsilə məlumat ötürülməsi üçün Zynq İşləmə Sistemini qurun

- Addım 6: Ethernet vasitəsilə məlumat qəbulu üçün Zynq İşləmə Sistemini qurun

- Addım 7: Zybo lövhələrinizi HDMI mənbəyinə və HDMI yuvasına qoşun

- Addım 8: Təkmilləşdirmə üçün alternativ fikirlər

- Addım 9: Əlçatanlıq

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:46.

- Son dəyişdirildi 2025-01-23 12:54.

Televizorunuzu xarici bir monitor olaraq bir kompüterə və ya dizüstü kompüterə bağlaya biləcəyinizi arzuladınızmı, amma bütün bu sinir bozucu kordonlara mane olmaq istəmədinizmi? Əgər belədirsə, bu təlimat yalnız sizin üçündür! Bu məqsədə çatan bəzi məhsullar olsa da, bir DIY layihəsi daha məmnun və potensial olaraq daha ucuzdur.

Bu konsepsiya, axın cihazı olmaq əvəzinə bir monitöre qoşulan bir HDMI kabelinin yerini tutmaq üçün nəzərdə tutulduğundan, chromecast kimi məhsullardan fərqlidir.

Layihəmiz, Kaliforniya Dövlət Politexnik Universiteti, San Luis Obispoda Real Zaman Əməliyyat Sistemləri kursu üçün son layihə olaraq yaradılmışdır.

Layihənin məqsədi, bir HDMI ötürücü cihazı (PC, blu-ray və s.) İlə HDMI qəbuledici qurğu (Masaüstü Monitor, Projektor, TV və s.) Arasında simsiz rabitə interfeysi rolunu oynamaq üçün iki Digilent Zybo lövhəsindən istifadə etməkdir.

Bir Digilent Zybo HDMI vasitəsilə ötürücü cihaza, digəri isə HDMI vasitəsilə qəbuledici cihaza qoşulacaq.

Simsiz rabitə, ev yönləndiricisi və ya başqa bir cihaz vasitəsi ilə ötürülmədən ötürücü və alıcıya ayrılmış simsiz lokal şəbəkə istifadə etməklə həyata keçiriləcəkdir. Bu layihə üçün istifadə olunan simsiz modul tplink wr802n nanorouterdir, onlardan biri şəbəkəni qurmaq üçün bir giriş nöqtəsi, digəri isə şəbəkəyə qoşulmaq üçün müştəri olaraq fəaliyyət göstərir. Hər bir nanorouter, Ethernet kabeli ilə ya Zybo lövhəsinə bağlanacaq. Bu marşrutlaşdırıcılara qoşulduqda, cihazlar tək bir Ethernet kabeli ilə bağlanmış kimi TCP vasitəsilə əlaqə quracaqlar (əlaqə qurmaq üçün lazım olan yeganə konfiqurasiya müştərinin IP ünvanıdır).

Layihənin məqsədi 60 Hz -də 1080x720 video axını asanlaşdırmaq olsa da, simsiz şəbəkədə bant genişliyi məhdudiyyətləri və göndərmək üçün lazım olan məlumatları azaltmaq üçün real vaxtda video sıxılma olmaması səbəbindən buna nail olmaq mümkün deyildi. Bunun əvəzinə, bu layihə, HDMI məlumatlarını nəzərdə tutulduğu kimi düzgün şəkildə yaymaq üçün çərçivə sürətində məhdudiyyətləri ciddi şəkildə məhdudlaşdırdığı üçün bu məqsədə çatmaq üçün gələcək inkişaf üçün bir çərçivə rolunu oynayır.

Layihə tələbləri:

2x Digilent Zybo İnkişaf Lövhələri (ən azı bir HDMI portu olmalıdır)

2x HDMI kabelləri

2x microusb kabelləri (inkişaf üçün Zybo'yu PC -yə bağlamaq üçün)

2x tplink wr802n nanorouterlər (adtl. 2x microusb və divar prizi güc adapterləri daxil olmaqla)

2x Ethernet kabelləri

*** Qeyd: Bu dərslikdə Vivado dizayn dəsti ilə tanışlıq və yeni bir layihə və blok dizaynı yaratmaq təcrübəsi nəzərdə tutulur. ***

Addım 1: Verici üçün Zynq Proqramlaşdırıla bilən Məntiqi konfiqurasiya edin

Vericinin proqramlaşdırıla bilən məntiqini inkişaf etdirmək üçün yanaşmamız, biri yazmaq, biri də oxumaq üçün iki Video Direct Memory Access (VDMA) blokundan istifadə etməklə kompüterdən izləmək üçün hdmi-hdmi keçidini həyata keçirmək idi.

Hər ikisi də sərbəst işləyən, 3 çərçivə tampon rejimi (0-1-2) üçün seçilir. Video nüvəsi saniyədə 60 kadr üçün optimallaşdırıldığı üçün bu, VDMA -nın hər 16,67 ms -də bu qaydada yeni bir çərçivəyə yazacağı və ya oxuyacağı deməkdir: 0, 1, 2, 0, 1, 2, 0, 1, 2. Hər bir çərçivə üçün DDR yaddaş yerləri iki VDMA üçün fərqlidir, çünki onlar artıq bir -biri ilə sinxronizasiya olunmur. Bunun əvəzinə, məlumatların iki yaddaş yeri arasında hərəkətini sinxronizasiya etmək üçün 60 Hz üçün konfiqurasiya edilmiş bir hardware timer (TTC1) istifadə olunur.

Yuxarıdakı şəkil 3 çərçivəni, ölçülərini və hər birinin tələb etdiyi yaddaş miqdarını göstərir (çərçivənin sağında). Yazma VDMA -nı bu yaddaş yerlərinə təyin etsək, 0x0B000000 ilə başlayaraq deyək ki, bu dəstdən kənarda oxunan VDMA yaddaş yerlərini təyin edə bilərik. Hər bir çərçivə 1280*720 pikseldən və hər piksel 8 bit qırmızı, yaşıl və göydən ibarət olmaqla 24 bit təşkil edir. Bu o deməkdir ki, bir çərçivə 1280*720*3 baytdan (2.76 MB) ibarətdir.

VDMA sürücü quruluşunda təsvir edilən IRQ taymerinin içərisində iki VMDA yaddaş yeri arasında məlumatların kopyalanması idarə ediləcək. VDMA, yazılan və ya oxunan cari çərçivəyə işarədir. Çərçivə, proqrama çevrilən müəyyən bir boz kodla təmsil olunur. 3 çərçivəli tampon konfiqurasiya üçün boz kod tərifləri AXI VDMA Məhsul Bələdçisində əlavə C-də tapıla bilər.

Bu, hazırda yazılan çərçivədən oxumadan yaddaşa yazılanları kopyalamağa imkan verir.

*** Qeyd edək ki, oxunan VDMA simsiz şəbəkə üzərindən məlumat göndərərkən istifadə edilmir. Yalnız məqsəd, yazma VMDA -dan yaddaşın kopyalanmasının düzgün işlədiyini yoxlamaqdır. Oxunan VMDA deaktiv edilməlidir.

Transmitter Dizayn Blokunu yaratmaq üçün addımlar:

- Yeni bir layihə hazırlayarkən, layihəyə bir çip və ya lövhə təyin etmək yaxşı bir fikirdir. Bu keçid, Vivado qovluğuna yeni lövhə fayllarının necə əlavə ediləcəyini və doğru lövhəni layihənizlə necə əlaqələndirəcəyinizi izah edir. Qenerasiya Sistemi blokunu əlavə edərkən və aparatdan proqrama keçərkən (SDK tərəfi) faydalı olacaq.

-

Aşağıdakı blokları əlavə edin:

- dvi2rgb

- Axi4 axınına video

- Zaman nəzarətçisi

- axi4-axını çıxarmaq

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Saat Sihirbazı

- Sabit

- Zynq İşləmə Sistemi

- Qenerasiya Sistemini əlavə edərkən, yuxarı yaşıl rəngli çubuqdan "Blok Avtomatlaşdırmasını Çalışdır" düyməsini basın və "Lövhə Hazır Ayarını Tətbiq et" seçiminin seçildiyinə əmin olun. Qalan hər şeyi standart olaraq qoyun.

- Hər bir blok konfiqurasiya pəncərəsinin şəkillərini yuxarıdakı şəkillərdə tapa bilərsiniz. Xüsusi bir pəncərə üçün bir şəkil görmürsənsə, onu standart olaraq buraxın.

-

Zynq Qenerasiya sistemini konfiqurasiya etməyə başlayın:

- PS-PL Konfiqurasiyasında AXI Qeyri-Təhlükəsiz Təhlükəsiz GP Master AXI-ni aktivləşdirin, M AXI GP0 İnterfeysini aktiv edin

- PS-PL Konfiqurasiyasında HP Slave AXI Arayüzü, həm HP0, həm də HP1-i aktiv edin

- MIO Konfiqurasiyasında ENET0 -un I/O Periferik Cihazları altında, sonra Tətbiq Prosessor Birimində, Timer0 -i aktiv etdiyinə əmin olun.

- Clock Configuration PL Fabric Clocks -da FCLK_CLK0 -ı aktiv edin və 100 MHz -ə təyin edin.

- Ok düyməsini basın

- "Bağlantı Otomasyonunu Çalıştır" ı tıklamadan əvvəl, video bloklarını yuxarıdakı TX blok dizaynında gördüyünüz kimi bağladığınızdan əmin olun. Sabitin adını VDD olaraq dəyişmək və dəyəri 1 olaraq təyin etmək istəyəcəksiniz. Video bloklarını buna uyğun olaraq bağlayın.

- HDMI TMDS saatını və məlumat pinlərini rgb2dvi və dvi2rgb bloklarında kənarlaşdırın

- Qaynar fiş aşkarlama siqnalı (HPD) üçün giriş və çıxış portu yaradın və onları bir -birinə bağlayın, bunlar məhdudiyyətlər sənədində müəyyən edilmişdir

-

Piksel saatı məhdudiyyətlər faylında yaradılan TMDS_Clk_p -dən bərpa olunur. Bu 720p qətnaməyə uyğun olaraq 74.25 MHz olacaq. Piksel saatını (dvi2rgb blokundan) aşağıdakı pinlərə bağlamaq vacibdir:

- vid_io_in_clk (axi axın blokuna daxil olun)

- vid_io_out_clk (axını axını blokdan çıxarmaq üçün)

- clk (Zamanlama Nəzarətçisi)

- PixelClk (rgb2dvi)

- *** Qeyd: Hal -hazırda, piksel saat bərpasını aktivləşdirmək üçün, HDMI rx və tx bağlayıcıları aktiv bir qaynağa/lavaboya bağlanmalıdır. Bunun bir yolu, video rx və tx bloklarını fərqli saat sahələrinə ayırmaqdır (başqa sözlə, tx blokuna qidalandırmaq üçün yeni 74.25 MHz saat yaratmaq). ***

- Sonra 100 MHz giriş (qlobal tampon mənbəyi) və 50 MHz-də 3 çıxış saatı (AXI-Lite saatı), 150 MHz (AXI4-Axın saatı), 200 MHz (dvi2rgb RefClk pin) üçün saat sihirbazını qurun.

- FCLK_CLK0 emal sistemi pinini saat sihirbazının girişinə qoşun

- Bu nöqtədə, dizayn pəncərəsinin yuxarısındakı yaşıl çubuqdan "Bağlantı Otomasyonunu Çalıştır" düyməsini basın. Bunu bir blok üçün etmək və yuxarıdakı TX blok dizayn görüntüsünü izləmək yaxşı bir fikirdir.

- Alət, AXI-Lite avtobusunu (VDMA və GPIO) istifadə edən bloklar üçün master/slave ara bağlantısı rolunu oynayan AXI Interconnect əlavə etməyə çalışacaq.

- VDMA (Stream to Memory Map və ya əksinə) tərəfindən istifadə olunan AXI4-Stream və Yüksək Performanslı prosessor interfeysləri üçün master/slave interconnect rolunu oynayan AXI SmartConnect də əlavə edəcək.

- Alət eyni zamanda bir Prosessor Sistem Sıfırlamasını da əlavə edəcək. Bunun yalnız VDMA, GPIO və prosessorla əlaqəli bloklara bağlı olduğundan əmin olun. Heç bir video blokuna bağlamayın (yəni dvi2rgb, zaman tənzimləyicisi, axın üçün vid və s.)

- Bağlantıların avtomatlaşdırılması başa çatdıqdan sonra, əlaqələrin TX blok dizayn şəkli ilə uyğun olduğunu yoxlayın. Qeyd edilməmiş əlavə bir Sistem ILA blokunu görəcəksiniz. Bu yalnız ayıklama üçündür və hələlik lazım deyil. 150M Prosessor Sıfırlamasından istifadə edir, buna görə də buna ehtiyac yoxdur. Avtobuslarda kiçik yaşıl "böcəklər" gördüyünüz hər yerdə, bu ILA səbəbiylədir və nəzərə alınmır.

- Son addım, layihə mənbələri ağacındakı blok dizaynına sağ vurmaq və "HDL Sarıcı Yarat" ı seçməkdir. Sarğıya məntiq əlavə etməyi planlaşdırırsınızsa, bu hər dəfə seçildikdə üzərinə yazılacaq.

- SDK tərəfindəki detallar üçün VDMA Sürücü Quraşdırma bölümünə baxın.

Saatlar və sıfırlamalar

Hər hansı bir proqramlaşdırıla bilən məntiq layihəsinin ən vacib cəhətlərinin saat sahələrini diqqətlə nəzərdən keçirmək və siqnalları sıfırlamaq olduğunu gördüm. Düzgün qurulubsa, dizaynınızı işə salmaq üçün yaxşı bir şansınız var.

Piksel Saatı və Zamanlama Kilidli

Bəzi siqnalların aktiv olduğunu yoxlamaq üçün bu siqnalları LED -lərə bağlamaq yaxşı olar (saatlar, sıfırlamalar, kilidlər və s.). Verici lövhəsində izləməyi faydalı hesab etdiyim iki siqnal, piksel saatı və AXI4-Stream-dən video çıxışı blokundakı "kilidli" siqnal idi ki, bu da videonun vaxt tənzimləyicisi və video mənbəyi ilə sinxronlaşdırıldığını bildirir. məlumatlar. Dvi2rgb blokundakı PixelClkLocked siqnalını sıfırlama olaraq istifadə edərək piksel saatını izləyən dizayn bloku sarmağına bir məntiq əlavə etdim. Faylı burada hdmi_wrapper.v olaraq əlavə etdim. Məhdudiyyətlər faylı da bura əlavə olunur.

Addım 2: Alıcı üçün Zynq Proqramlaşdırıla bilən Məntiqi konfiqurasiya edin

Alıcı üçün Proqramlaşdırıla bilən Məntiq bloku daha sadədir. Eksik hdmi giriş bloklarından başqa əsas fərq, bərpa edilmiş piksel saatının olmamasıdır. Bu səbəbdən saat sihirbazından özümüzü yaratmalıyıq. Bu dizayn vericidən ayrı bir layihədə edilməlidir. Bizim məqsədlərimiz üçün alıcı layihə Zybo 7Z-20 lövhəsini, verici isə Z7-10 lövhəsini izlədi. Lövhələrdəki FPGA -lar fərqlidir, buna görə diqqətli olun.

Alıcı Dizayn Blokunu yaratmaq üçün addımlar:

-

Dizaynınıza aşağıdakı ip bloklarını əlavə edin:

- Zaman nəzarətçisi

- AXI4-Video Çıxışına axın

- RGB -dən DVI -yə

- AXI VDMA

- AXI GPIO

- Qenerasiya Sistemi

- Saat Sihirbazı

- Sabit (VDD 1 olaraq təyin olunur)

- Bu blokları Transmitter kimi konfiqurasiya etmək üçün eyni nümunəni izləyin. Konfiqurasiyada nəzərəçarpacaq fərqlər üçün şəkillər bura daxil edilmişdir. Qalanları Verici ilə eyni qalır.

- Bu dizayn üçün VDMA -nı yalnız oxunan kanal olaraq konfiqurasiya edin. Yazı kanalını deaktiv edin.

-

Saat sihirbazı aşağıdakı çıxışlar üçün konfiqurasiya edilməlidir:

- clk_out1: 75 MHz (piksel saatı)

- clk_out2: 150 MHz (axın saatı)

- clk_out3: 50 MHz (axi-lite saat)

- Video bloklarını RX blok dizaynında göstərildiyi kimi bağlayın.

- Sonra AXI Interconnect, AXI SmartConnect və System Reset bloklarını əlavə edəcək və müvafiq əlaqələr qurmağa çalışacaq bağlantı avtomatlaşdırmasını işə salın. İstənməyən bağlantılar yaratmadığından əmin olmaq üçün yavaş -yavaş bura gedin.

- HDMI TMDS saatını və məlumat pinlərini rgb2dvi blokunda kənarlaşdırın

- Bu dizaynda isti fiş siqnalına ehtiyac yoxdur.

Addım 3: VDMA Sürücüsünü qurun

AXI-Lite interfeysi vasitəsi ilə konfiqurasiya olunan fərqli bloklar üçün quraşdırma ən yaxşı şəkildə BSP-ə daxil edilmiş demo layihələrdən istifadə etməklə edilir. Dizayn aparatını ixrac etdikdən və Vivadodan SDK -nı işə saldıqdan sonra yeni bir lövhə dəstəyi paketi əlavə etmək və BSP parametrləri pəncərəsinə lwip202 kitabxanasını daxil etmək istəyəcəksiniz. System.mss faylını BSP -dən açın və blok dizaynınızdakı mövcud olan xarici sürücüləri görəcəksiniz. "Nümunələri İdxal et" seçimi, bu ətraf qurğulardan istifadə edən demo layihələrini idxal etməyə və bununla da mövcud Xilinx sürücülərindən istifadə edərək onları proqramda necə konfiqurasiya edəcəyinizi göstərməyə imkan verir (əlavə olunmuş şəklə baxın).

Bu, VDMA, Timer & Interrupt və GPIO -nu konfiqurasiya etmək üçün istifadə olunan üsuldur. Həm ötürmək, həm də qəbul etmək üçün mənbə kodu bura daxil edilmişdir. Fərqlər demək olar ki, yalnız main.c.

*** DİQQƏT: Sistem bu təlimatı yazarkən tam işləmədiyi üçün bu hissədəki mənbə kodu simsiz şəbəkə kodunu ehtiva etmir. Video çekirdek ötürmə/qəbul layihələrinin şəbəkə ötürmə/qəbul layihələri ilə birləşdirilməsi nəticəsində bir neçə səhv həll edilməlidir. Buna görə də, bu dərslik onları ayrı -ayrılıqda nəzərdən keçirir.

TX Interrupt Handler Function (IRQHandler)

Bu funksiya GPIO blokları vasitəsi ilə həm VDMA -nın oxunması, həm də yazılmasının təmin etdiyi boz kodları oxuyur. Boz kodlar onluğa çevrilir və cari çərçivənin çərçivə əsas yaddaş yerini seçmək üçün istifadə olunur. Kopyalanan çərçivə, VDMA tərəfindən yazılana əvvəlki çərçivədir (məsələn, VDMA 2 -ci çərçivəyə yazırsa, 1 -ci çərçivəni kopyalayırıq, 0 -a yazırıqsa, 2 -ci çərçivədən büküb oxuyuruq).

Çərçivə sürətini 60 Hz -dən 10 Hz -ə endirmək üçün funksiya yalnız hər 6 -cı kadrı çəkir. Şəbəkənin yuxarı həddi 300 Mbit / s -dir. Saniyədə 10 kadrda 221,2 Mbit / s bant genişliyi tələb olunur.

Bu funksiyada iki sətrin şərh edilməsi/şərh edilməməsi istifadəçiyə ayıklama/test məqsədləri üçün HDMI keçid rejiminə keçməyə imkan verəcək (kod müvafiq sətirləri göstərmək üçün şərh edilmişdir). Hal -hazırda çərçivəni ethernet kodunun istifadə etdiyi bir yaddaş yerinə kopyalayır.

RX Interrupt Handler Function (IRQHandler)

Bu funksiya TX funksiyasına çox bənzəyir, lakin daxil olan məlumatları yazmaq üçün Ethernet tərəfindən istifadə olunan 2 tampon FIFO -dan kopyalanır. Ethernet kodu, FIFO -ya hansı çərçivənin yazıldığını göstərir, məlumatlar əks çərçivədən kopyalanır. Məlumatlar yırtılmamaq üçün VDMA tərəfindən oxunan çərçivənin arxasındakı çərçivəyə kopyalanır.

Addım 4: Nanorouter Şəbəkəsini qurun

TPlink nanorouters istifadə edərək bir şəbəkə yaratmaq üçün onları ayrı -ayrılıqda işə salın və cihazlar üçün standart wifi SSID -ə qoşulun. Bu cihazın konfiqurasiya parametrləri haqqında daha çox məlumatı cihazın istifadəçi təlimatında tapa bilərsiniz.

Cihazlardan birini giriş nöqtəsi olaraq qurun, bu şəbəkə üçün əsas əlaqə rolunu oynayacaq. Şəbəkənin adını çəkdiyinizə və adını qeyd etdiyinizə və DHCP -ni deaktiv etdiyinizə əmin olun (marşrutlaşdırıcının IP ünvanlarını dinamik olaraq konfiqurasiya etməsini istəmirik, tansmitter və alıcı Zybo lövhələrinin IP ünvanlarını ardıcıl olaraq təyin etmələrini istəyirik). Konfiqurasiya etdikdən sonra cihazın yenidən başladığından və bu şəbəkəni qurduğundan əmin olun.

Digər cihazı müştəri olaraq qurun və ilk nanorouter ilə qurduğunuz SSID şəbəkəsinə qoşulduğundan əmin olun. Bir daha, müştəri üçün DHCP -nin əlil olduğundan əmin olun.

Müştəri bitirdikdən və yenidən başladıqdan sonra, nanorouter giriş nöqtəsinə qoşulmalıdır (əgər belə deyilsə, ehtimal ki, cihazlardan birinin konfiqurasiyasında bir problem var). Müştəri üzərindəki LED işığının giriş nöqtəsinə qoşulduqdan sonra möhkəm olacağını görəcəksiniz.

Giriş nöqtəsi nanorouter LED, ehtimal ki, bu nöqtədə yanıb -sönməyə davam edəcək, bu yaxşıdır! Yanıp sönən işıq, Ethernet portundan başqa bir cihaza qoşulmadığını bildirir və konfiqurasiya edilmiş Zybo -ya qoşulduqdan sonra LED sabit bir şəbəkə bağlantısı olduğunu göstərir.

İndi nanorouterlər qurduqdan sonra ünsiyyət qurmağımıza imkan verən simsiz şəbəkəmiz var. Nanorouterlər üçün (giriş nöqtəsi və müştəri kimi) konfiqurasiya metodumuz, ötürücü Zybo lövhəsindən alıcı Zybo lövhəsinə, hər ikisinin tək bir Ethernet teli ilə əlaqəli olduğu kimi ünsiyyət qurmağımıza imkan verir. Bu, şəbəkə quruluşumuzu daha da çətinləşdirir, çünki alternativ, ehtimal ki, nəzərdə tutulan əlaqə ilə birlikdə serverə açıq şəkildə qoşulmaq üçün Zybo lövhələrinin konfiqurasiyasını ehtiva edir.

Hər iki cihaz qurulduqdan sonra, nanorouterlər konfiqurasiya edilir və WIDI şəbəkənizdə tətbiq olunmağa hazırdır. Nanorouter və Zybo lövhələri arasında xüsusi bir cütləşmə yoxdur, çünki ya giriş nöqtəsi, ya da müştəri ya ötürmə, ya da qəbul cihazı üçün işləyəcək.

Addım 5: Ethernet vasitəsilə məlumat ötürülməsi üçün Zynq İşləmə Sistemini qurun

HDMI məlumatlarını bir Zybo lövhəsindən digərinə ötürmək üçün VDMA sürücümüzə bir Ethernet protokolu daxil etməliyik. Buradakı məqsədimiz, şəbəkə bant genişliyimizə uyğun gələn müəyyən bir sürətlə, işləmə sistemindəki Ethernet ətrafı vasitəsi ilə fərdi video çərçivələri yayımlamaqdır. Layihəmiz üçün çılpaq metal LwIP API tərəfindən təmin edilən TCP-dən istifadə etdik. Layihə üzvlərinin hər ikisi şəbəkə kommunal xidmətlərində nisbətən təcrübəsiz olduqları üçün bu seçim TCP ilə əlaqəli təsirləri və məhdudiyyətləri tam olaraq tanımadan edildi. Bu tətbiqin əsas problemi, məhdud bant genişliyi və həqiqətən də yüksək həcmli məlumatların buxarlanması üçün nəzərdə tutulmaması idi. TCP -ni əvəz etmək və bu layihəni yaxşılaşdırmaq üçün alternativ həllər daha sonra müzakirə olunacaq.

LwIP ilə TCP -nin qısa təsviri: Məlumat şəbəkə üzərindən tcp_mss (TCP maksimum seqment ölçüsü) paketlərində göndərilir, bu da ümumiyyətlə 1460 baytdır. Tcp_write -a zəng etmək, göstərici tərəfindən istinad edilən bəzi məlumatları alacaq və məlumatları saxlamaq və TCP əməliyyatları üçün bir quruluş təmin etmək üçün pbufs (paket tamponları) quracaq. Bir anda növbə çəkilə bilən maksimum məlumat miqdarı tcp_snd_buf (TCP göndərən tampon boşluğu) olaraq təyin olunur. Bu parametr 16 bitlik bir rəqəm olduğundan, 59695 baytlıq bir göndərmə bufer ölçüsü ilə məhdudlaşırıq (göndərmə tamponunda bəzi lazımi doldurma var). Məlumatlar növbə çəkildikdən sonra, məlumatların ötürülməsinə başlamaq üçün tcp_output çağırılır. Növbəti məlumat seqmentini göndərməzdən əvvəl əvvəlki paketlərin hamısının uğurla ötürülməsi vacibdir. Bu proses recv_callback funksiyasından istifadə etməklə həyata keçirilir, çünki bu qəbuledicidən təsdiq görünəndə çağırılır.

Vivado SDK -da nümunə layihələrdən istifadə etmək, LwIP TCP əməliyyatının öyrənilməsində çox faydalıdır və yeni bir layihəyə başlamaq üçün yaxşı bir başlanğıc nöqtəsidir.

WiDi ötürücü qurğunun proseduru belədir:

- Çılpaq metal LWIP sürücü funksiyası zənglərindən istifadə edərək TCP şəbəkəsini işə salın.

- Şəbəkə əməliyyatları üçün lazım olan hər hansı bir geri çağırma funksiyasını göstərin.

- WiDi qəbuledicisinə IP ünvanına və portuna qoşularaq qoşulun (konfiqurasiyamız: Alıcı IP 192.168.0.9, 7 porta qoşulun).

- VDMA sürücü taymeri başa çatdıqda, TX ISR daxil edin.

- VDMA boz koduna əsasən daxil olmaq üçün mövcud çərçivə tamponunu təyin edin

- TCP göndərmə tamponunda məlumatların birinci seqmentini sıraya qoyun

- Verilənləri çıxarın və cari çərçivədən nə qədər məlumat göndərildiyini izləmək üçün yerli dəyişənləri yeniləyin.

- Alınan geri çağırışa çatdıqda (ötürücü məlumatların alındığını təsdiqlədikdən sonra edilən funksional zəng), məlumatların növbəti seqmentini sıraya qoyun.

- Bütün çərçivə göndərilənə qədər 7 və 8 -ci addımları təkrarlayın.

- Yeni bir çərçivənin hazır olduğunu göstərmək üçün növbəti taymerin kəsilməsini gözləmək üçün boş bir vəziyyətə qayıdın (4 -cü addıma qayıdın).

LwIP lövhə dəstəyi paketini yuxarıdakı şəkildə göstərildiyi kimi qurduğunuzdan əmin olun. Tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg istisna olmaqla, bütün dəyərlər standartdır. Ayrıca, debug_options qrupu üçün BSP parametrlərini dəyişdirməklə ətraflı ayıklama əldə edilə biləcəyini unutmayın.

Addım 6: Ethernet vasitəsilə məlumat qəbulu üçün Zynq İşləmə Sistemini qurun

Simsiz qəbuledici rolunu oynayacaq Zybo inkişaf lövhəsi də ötürücü qurğuya bənzər şəkildə işləyəcək. LwIP üçün lövhə dəstəyi paketi parametrləri əvvəlki addımdakılarla eyni olacaq.

Cihaz nanorouterdən video çərçivə seqmentləri olan paketləri alacaq və video çərçivə məlumatlarını qəbul edən VDMA üçün üçlü çərçivə tampon boşluğuna kopyalayacaq. Hər hansı bir məlumatın üstünə yazılmaması üçün, nanorouterdən məlumat toplayarkən ikiqat məlumat buferi (şəbəkə tamponu olaraq adlandıracağıq) istifadə olunur ki, əvvəlki tam video çərçivəsi kopyalanarkən şəbəkə trafiki axını davam etdirə bilsin. VDMA tamponu.

WiDi qəbuledici qurğunun proseduru iki vəzifəni tələb edir, onlardan biri ethernet məlumatlarını alır, digəri isə video çərçivələri şəbəkə buferindən VDMA -nın üçlü çərçivə buferinə kopyalayır.

Ethernet qəbulu vəzifəsi:

- Çılpaq metal LWIP sürücü funksiyası zənglərindən istifadə edərək TCP şəbəkəsini işə salın (ötürücünün qoşulacağı IP ünvanı ilə quraşdırma, bizimki 192.168.0.9)

- Şəbəkə əməliyyatları üçün lazım olan hər hansı bir geri çağırma funksiyasını göstərin.

- Ethernet paketini aldıqdan sonra paket məlumatlarını cari şəbəkə tamponuna kopyalayın, cari yığılmış məlumatları artırın.

- Paket şəbəkə çərçivə tamponunu doldurursa, 5 və 6 -cı addımlara davam edin. Əks təqdirdə, bu vəzifədən 3 -cü addıma geri dönün.

- VDMA üçlü çərçivə tampon vəzifəsinin yeni bitmiş şəbəkə tamponundan kopyalanması lazım olduğuna işarədir.

- Digər şəbəkə tamponuna keçin və Ethernet vasitəsilə məlumat toplamağa davam edin.

- Yeni Ethernet paketi alınana qədər boş qalın (addım 3).

Şəbəkə tamponunu VDMA üçlü çərçivə buferinə kopyalayın:

- VDMA sürücü taymeri başa çatdıqda, RX ISR daxil edin.

- VDMA boz koduna əsasən daxil olmaq üçün mövcud çərçivə tamponunu təyin edin.

- VDMA tamponuna hansı şəbəkə tamponunun kopyalanacağını təyin edin və həmin məlumatları kopyalayın

Addım 7: Zybo lövhələrinizi HDMI mənbəyinə və HDMI yuvasına qoşun

İndi həm alıcı, həm də ötürücü üçün hdmi kabellərini bağlayın, FPGA -ları proqramlaşdırın və emal sistemini işə salın. LwIP əməliyyatında böyük xərc və məhdud bant genişliyi səbəbiylə kadr sürəti çox yavaş olacaq. Hər hansı bir problem varsa, UART vasitəsilə əlaqə qurun və hər hansı bir xəbərdarlıq və ya səhv müəyyən etməyə çalışın.

Addım 8: Təkmilləşdirmə üçün alternativ fikirlər

Bu layihə üçün böyük bir problem, wifi üzərindən göndərmək üçün lazım olan məlumatların miqdarı idi. Bu gözlənilən idi, ancaq bunun təsirini qiymətləndirmədik və bir video axını deyil, ekranda daha çox görüntü partlaması ilə nəticələndik. Bu layihəni təkmilləşdirməyin bir neçə yolu var:

- Real vaxtda video sıxılma. Gələn video feed çərçivəsini çərçivəyə sıxmaq şəbəkə üzərindən göndərilməli olan məlumatların miqdarını xeyli azaldacaq. İdeal olaraq bu, aparatla edilə bilər (bu asan bir iş deyil) və ya bir sıxılma alqoritmini işə salmaq üçün digər ARM nüvəsindən istifadə etməklə proqram təminatında edilə bilər (bunun üçün vaxtın işləməsini təmin etmək üçün bir az daha təhlil lazımdır). İnternetdə tapdığımız bəzi açıq mənbəli real vaxt video sıxılma komponentləri var, lakin əksəriyyəti IP -dir.

- Ethernet axınının proqram təminatında deyil, aparatda tətbiqi. Segmentin ölçüsünün məhdudlaşdırılması səbəbindən ötürücüdə gedən məlumatları növbə etmək üçün yer olmadığı üçün bir ton əlavə xərc var idi. AXI Ethernet IP -ni FIFO tamponu və ya DMA ilə istifadə edərək məlumatları daxil etmək daha təsirli bir prosesdir. Bu, LwIP TCP -dən əlavə baqajı azaldar və daha çox məlumat axını təmin edər.

Addım 9: Əlçatanlıq

Bu WiDi layihəsinin məhsulu, istifadəçinin hər hansı bir HDMI mənbəyinə qoşula biləcəyi və sonra video ötürməsini HDMI qabiliyyəti olan bir ekrana batıra biləcəyi tam inteqrasiya edilmiş, kompakt bir cüt cihaz olmalıdır. Cihazlar Zybo istinad lövhəsində tapılan Zynq-7000 SoC-yə malik olacaq və TP-Link nano-marşrutlaşdırıcılarında olan şəbəkə avadanlıqlarını özündə birləşdirəcək. İdeal olaraq, istifadəçi, əhəmiyyətli texniki qabiliyyətə az ehtiyac duyaraq, ötürmə modulunu hədəf əməliyyat sistemi daxilində ayrı bir yerdən idarə edə bilər.

Təhlükəsizlik və Bağlantı

Cihazlar həm də Məxfilik məqsədləri üçün Nəqliyyat Layer Təhlükəsizliyi (TLS) daxil etməli və məhdud avtomatik əlaqə qabiliyyətinə malik olmalıdır. Dizaynerlərin, həssas materialı səhvən yaymamaq üçün simsiz interfeys üzərindəki bir ekranla əlaqəni istifadəçi adına qəsdən bir hərəkət etmək niyyəti var.

Hazırkı Vəziyyət

Bu vaxta qədər layihənin vəziyyəti hələ çox davam edir. Mövcud son nöqtə istifadəçisinin bu dərsdən faydalanması üçün, quraşdırılmış sistem dizaynı haqqında güclü texniki anlayışa malik olmalı və proqramlaşdırıla bilən aparat və quraşdırılmış proqram təminatı ilə bir yerdə tanış olmalıdır.

Şəbəkə üzərindən göndərilən məlumatlar bu anda şifrələnmir və TCP/IP paketlərinin xam ötürülməsi olduğu güman edilir.

Video çekirdek layihəsi həm ötürmə, həm də qəbul üçün uğurla sınaqdan keçirildi. Digər tərəfdən, iki zybo lövhəsi arasında simsiz əlaqə quruldu və test çərçivə məlumatları uğurla göndərildi. Bununla birlikdə, hər bir video nüvə layihəsinə şəbəkə kodunu birləşdirmək və faktiki video çərçivələrinin ötürülməsini yoxlamaq lazımdır.

Tövsiyə:

DIY ESP32 İnkişaf Lövhəsi - ESPer: 5 addım (şəkillərlə birlikdə)

DIY ESP32 İnkişaf etdirmə Şurası - ESPer: Bu yaxınlarda bir çox IoT (Əşyaların İnterneti) haqqında oxuyurdum və mənə inanırdım, sadəcə internetə qoşulma qabiliyyətinə malik olan bu gözəl cihazlardan birini sınamaq üçün gözləyə bilmirdim. özüm və əlimi işə götür. Xoşbəxtlikdən bir fürsət

Arduino UNO istifadə edərək pilotsuz təyyarə necə etmək olar - Mikrokontrolördən istifadə edərək bir Quadcopter hazırlayın: 8 addım (şəkillərlə)

Arduino UNO istifadə edərək pilotsuz təyyarə necə etmək olar | Mikrokontrolördən istifadə edərək Quadcopter hazırlayın: Giriş Youtube Kanalımı Ziyarət Edin Drone almaq üçün çox bahalı bir gadget (məhsul) təşkil edir. Bu yazıda necə ucuz satacağımı müzakirə edəcəyəm? Ucuz qiymətə öz əlinizlə bunu necə edə bilərsiniz … Yaxşı Hindistanda bütün materiallar (mühərriklər, ESClər

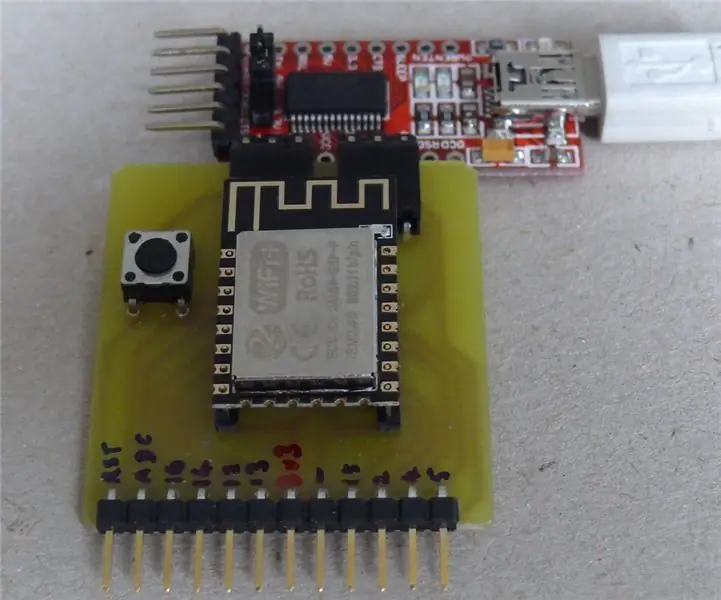

ESP-12E və ESP-12F Proqramlaşdırma və İnkişaf Lövhəsi: 3 addım (şəkillərlə)

ESP-12E və ESP-12F Proqramlaşdırma və İnkişaf Lövhəsi: Bu lövhənin vəzifəsi sadə idi: ESP-12E və ESP-12F modullarını NodeMCU lövhələri kimi asanlıqla proqramlaşdıra biləsiniz (yəni düymələrə basmağa ehtiyac yoxdur). İstifadə edilə bilən IO -ya çıxışı olan çörək taxtası dostu pinlərə sahib olun. Serial ötürmək üçün ayrı bir USB istifadə edin

UDuino: Çox Ucuz Arduino Uyğun İnkişaf Lövhəsi: 7 Addım (Şəkillərlə birlikdə)

UDuino: Çox Ucuz Arduino Uyğun İnkişaf Kartı: Arduino lövhələri prototip hazırlamaq üçün əladır. Eyni vaxtda birdən çox layihəniz olduqda və ya daha böyük bir layihə üçün çoxlu nəzarətçi lövhələrinə ehtiyacınız olduqda olduqca bahalı olurlar. Bəzi əla, daha ucuz alternativlər var (Boarduino, Freeduino), amma

LCD ilə Atmega16/32 İnkişaf Lövhəsi: 8 addım

LCD ilə Atmega16/32 İnkişaf Lövhəsi: Bu təlimat Atmega16 və ya Atmega32 prosessorları üçün öz inkişaf lövhənizi necə edəcəyinizi göstərir. İnternet evdə hazırlanan inkişaf lövhələri ilə doludur, amma düşünürəm ki, başqa birinə yer qaldı. Bu lövhə layihəmdə çox faydalı oldu