Mündəricat:

- Müəllif John Day day@howwhatproduce.com.

- Public 2024-01-30 07:44.

- Son dəyişdirildi 2025-01-23 12:54.

Bu qalxan ilə Mojo inkişaf lövhənizi xarici girişlərə qoşun.

Mojo inkişaf lövhəsi nədir?

Mojo inkişaf lövhəsi, Xilinx spartan 3 FPGA ətrafında qurulmuş bir inkişaf lövhəsidir. Lövhə Alchitry tərəfindən hazırlanmışdır. FPGA -lar, birdən çox prosesin eyni anda icra edilməli olduğu yerlərdə çox faydalıdır.

Nəyə ehtiyacınız olacaq?

Təchizat

Mojo inkişaf lövhəsi

Gerber faylı

8 x 15k ohm rezistorlar (isteğe bağlı*)

4 x 470 ohm rezistorlar

4 x 560 ohm rezistorlar

4 x CC yeddi seqmentli ekranlar

4 x 3 mm LED

4 x SPDT toxunma açarları

1 x 4 mövqe səthə montaj DIP açarı

2 x 25 x 2 və ya 4 x 25 başlıqlar

1 x 2 x 5 pinli qutu başı

Lehimleme dəmir

Lehim

Flux

*(bu rezistorlar buraxılırsa, müvafiq pinlər üçün daxili çəkmə/açma aktivləşdirilməlidir)

Addım 1: Gerberi Seçdiyiniz Pcb İstehsalçısına Yükləyin

Lövhələrim üçün JLC PCB -dən sifariş verdim.

Etdiyim yeganə dəyişiklik Mojo qarasına uyğun gəlmək istədiyim rəng idi.

Addım 2: İdarə Heyətinin Qurulması

Lehim edərkən həmişə ən aşağı hissələri lehimləməyi faydalı hesab edirəm, buna görə rezistorlardan başlamaq yaxşı bir fikirdir.

R5, R6, R7, R8, R9, R10, R11 və R12, açarları aşağı çəkmək üçün istifadə olunan 15k ohm rezistorlardır (daxili çəkmə/açma istifadə edirsinizsə, buna məhəl qoymayın).

R1, R2, R3, R4, 7 seqmentli ekran vasitəsilə cərəyanı məhdudlaşdırmaqdan məsul olan 560 ohm rezistorlardır.

R13, R14, R15, R16, 4 LED -dən axını məhdudlaşdırmaqdan məsul olan 470 ohm rezistorlardır.

Sonrakı daldırma açarı, toxunma açarları, LEDlər, yeddi seqmentli ekranlar və qutu başlığı konnektoru.

İndi pinləri hizalamaq üçün 25 -i 2 -yə (və ya 2 -ə 25 -ə 1) qoyun. Qalxanı sancaqlar ilə hizalayın və yerinə lehimləyin.

Addım 3: Proqram Quraşdırması

Alchitry veb saytına istinad edən proqramlar üçün Xilinx ISE -ni işə salmaq və qurmaq üçün nələr lazım olduğunu sizə xəbər verəcəyik. Bununla birlikdə.ucf faylını dəyişdirərək proqramınızı işə salmaq üçün vacib olanların hansı pinlərlə əlaqəli olduğunu bilir.

Budur qalxanla birlikdə istifadə etdiyim.ucf faylı:

Konfiqurasiya VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" 50 MHz HIGH 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

. Ucf ilə pinləri düzəltmək üçün açılan rezistorları quraşdırmadığınızı unutmayın

| ASAĞI DARTMAQ, ALÇALDMAQ, AZALTMAQ; o

| PULLUP;

Bloku bir şey üçün istifadə etmək istəyirsinizsə əlaqələr aşağıdakı kimidir. Solda blok pin nömrəsi və sağda.ucf -da təyin etməli olduğunuz mojo pin nömrəsi:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

Tövsiyə:

Arduino və digər mikrosxemlər üçün daha ucuz bir ESP8266 WiFi qalxanı: 6 addım (şəkillərlə)

Arduino və digər mikrosxemlər üçün daha ucuz bir ESP8266 WiFi qalxanı: Yeniləmə: 29 oktyabr 2020 ESP8266 lövhə kitabxanası V2.7.4 ilə sınaqdan keçirildi - Yeniləmə: 23 sentyabr 2016 Bu layihə üçün Arduino ESP lövhə kitabxanası V2.3.0 -dan istifadə etməyin. V2.2.0 işləri Güncəlləmə: 19 May 2016 Bu layihənin 14 -cü rübü kitabxanaları və kodu işləmək üçün yenidən nəzərdən keçirir

Mobil Nəzarətli Bluetooth Avtomobil -- Asan -- Sadə -- Hc-05 -- Motor qalxanı: 10 addım (şəkillərlə birlikdə)

Mobil Nəzarətli Bluetooth Avtomobil || Asan || Sadə || Hc-05 || Motor Qalxanı: … Zəhmət olmasa YouTube kanalıma ABUNƏ OL ………. Bu mobil ilə ünsiyyət qurmaq üçün HC-05 Bluetooth modulundan istifadə edən Bluetooth idarə olunan avtomobildir. Bluetooth vasitəsi ilə avtomobili mobil telefonla idarə edə bilərik. Avtomobilin hərəkətini idarə etmək üçün bir tətbiq var

Vokal GOBO - Səs Dampener Qalxanı - Vokal Booth - Vokal Qutu - Refleks Filtri - Vokalşield: 11 Addım

Vokal GOBO - Səs Dampener Shield - Vokal Booth - Vokal Box - Reflexion Filter - Vocalshield: Ev studiyamda daha çox vokal yazmağa başladım və daha yaxşı bir səs əldə etmək istədim və bəzi araşdırmalardan sonra " GOBO " idi. Bu səs söndürücü şeyləri görmüşdüm, amma nə etdiklərini anlamadım. İndi edirəm. Y tapdım

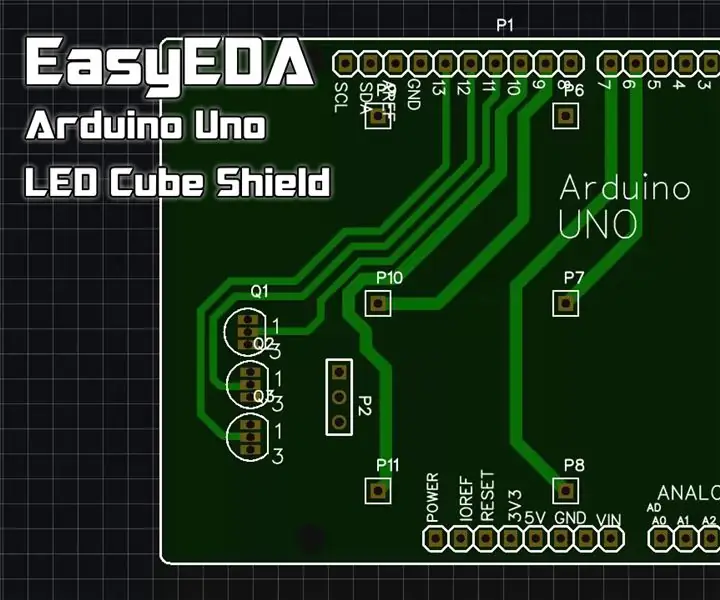

Arduino qalxanı necə çox asan yaradılır (EasyEDA istifadə edərək): 4 addım

Arduino qalxanı necə çox asan yaradılır (EasyEDA istifadə edərək): Bu təlimatda sizə çox asan bir Arduino Uno qalxanı yaratmağı öyrədəcəyəm. Çox detallara girməyəcəyəm, ancaq bir video Proqramı necə istifadə edəcəyinizi bir az daha dərindən öyrənin. EasyEDA veb tətbiqindən istifadə edirəm

Elektromaqnit heyəti: 4 addım (şəkillərlə)

Elektromaqnit heyəti: Bu layihə başqa bir şəkildə əldə edilə bilməyən ferromaqnit cisimlərə çatmağa kömək edir. Əlilliyi olan insanlara kömək etmək üçün istifadə edilə bilər, amma şəxsən özüm tikmişəm, çünki çox gözəl